#### CALIFORNIA STATE UNIVERSITY NORTHRIDGE

website

# Computer Org & ASSEMBLY Programming Apple SoC

Rev 8-1-24

email i jeffrey.drobman@csun.edu

- Apple History

- $\Box \quad \text{Early Computers} \rightarrow \text{slide 3}$

- □ Apple Company  $\rightarrow$  slide 10

- □ Apple Events  $\rightarrow$  slide 14

- iPhone 15  $\rightarrow$  slide 15

- M2 (WWDC)  $\rightarrow$  slide 15

- iPhones  $\rightarrow$  slide 36

- iPad  $\rightarrow$  slide 46

- Mac  $\rightarrow$  slide 55

- Apple ARM SoC's

- $\Box$  Apple A series  $\rightarrow$  slide 66

- □ Apple M series  $\rightarrow$  slide 101

- lacksquare Apple Chip Fab ightarrow slide 171

- Software

- MacOS  $\rightarrow$  slide 176

- iOS  $\rightarrow$  slide 179

Section

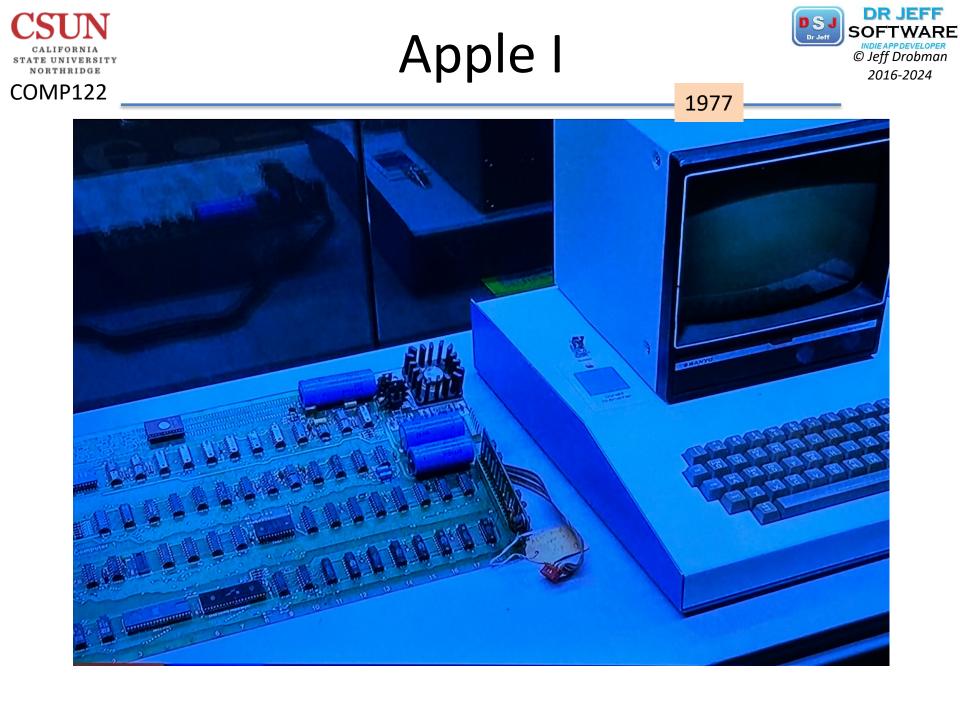

Early Apple Computers

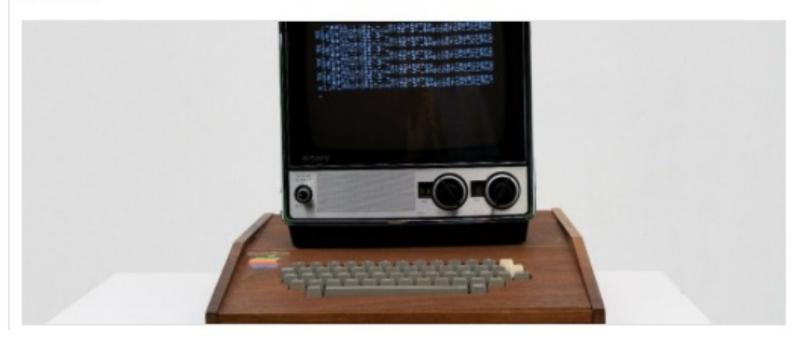

## **Original Apple I**

CALIFORNIA STATE UNIVERSITY NORTHRIDGE

**COMP122**

## **RARE APPLE COMPUTER UP FOR AUCTION**

6:19

70°

# Apple I Computer

Robert Mudry, Retired Silicon Valley engineering geek. Shared Feb 6

## A Hand-Built, Original Apple 1 Computer Is Yours for Just 1.5 Million Dollars

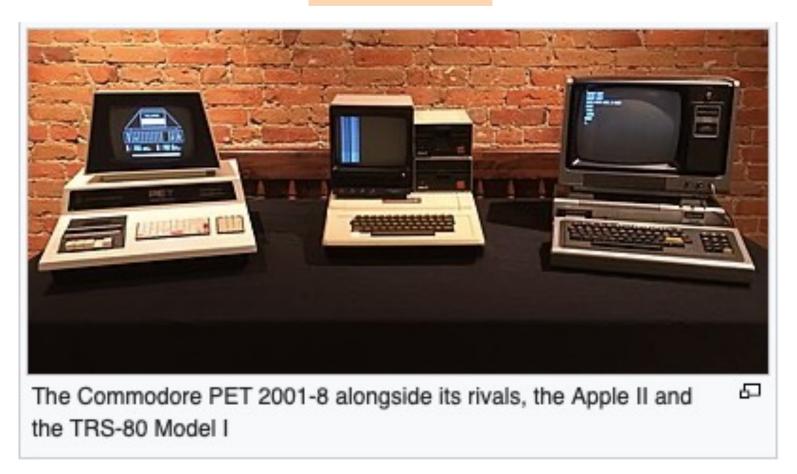

#### Commodore PET

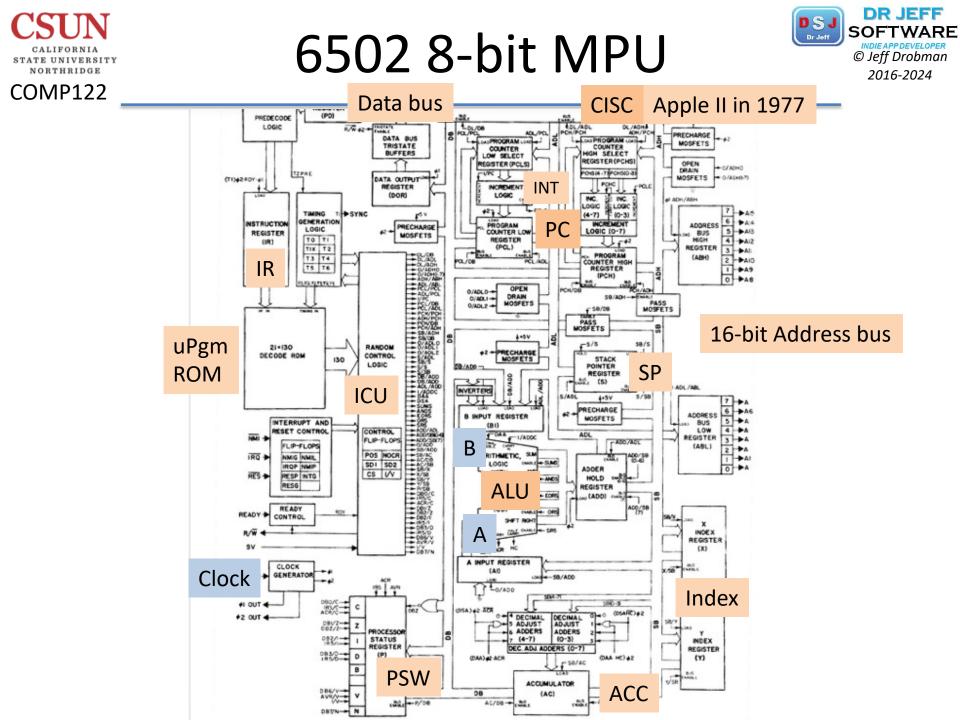

## 6502 8-bit MPU

#### Apple II in 1977 CISC

#### Other than ALU, what are the basic components of a CPU?

NORTHRIDGE

**COMP122**

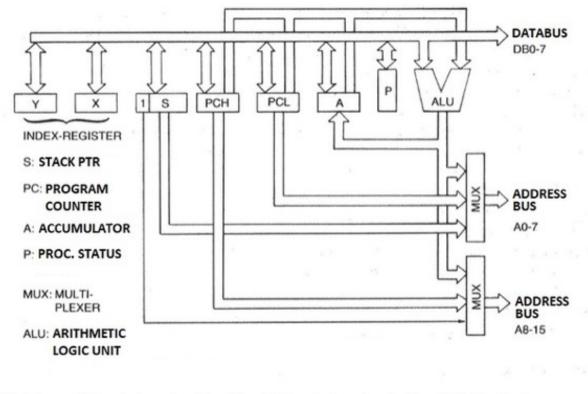

Most of the answers are for more complicated CPUs, with caches, pipelines, DMA etc. But the basic components for a working CPU are much fewer. The 8-bit 6502 microprocessor, introduced in 1975 and used in the Apple ][ computer and other early personal computers, had only 3510 transistors (compared to the many billions in today's CPUs). Its basic block diagram was fairly simple and easy to understand:

Not shown is the Instruction Register (IR) and decoder logic, which holds the instruction being executed which was fetched from memory.

# 6502 8-bit MPU

CISC Apple II in 1977 The 6502 had one 8-bit accumulator, and two 8-bit index registers, 8-bit stack pointer, and a 16-bit program counter so it could address a maximum of 65536 bytes.

| MOS 6502 registers |                 |                     |

|--------------------|-----------------|---------------------|

| FEDCBA98           | 7 6 5 4 3 2 1 0 | (bit position, hex) |

| Main registers     |                 |                     |

|                    | А               | Accumulator         |

| Index registers    |                 |                     |

|                    | х               | X index             |

|                    | Y               | Y index             |

| 00000001           | S               | Stack Pointer       |

| Program counter    |                 |                     |

| F                  | PC .            | Program Counter     |

| Status register    |                 |                     |

|                    | NV-BDIZC        | P Processor flags   |

ORTHRIDGE

**COMP122**

The high byte of the stack address is hardwired to 1, so stack addresses ranged from 0x1FF (initial value) to 0x100.

Section

ATE UNIVERSITY NORTHRIDGE

**COMP122**

Section

## **Apple Events**

# Apple Event September 12, 2023

## **View recent Apple events**

**WWDC** June 5, 2023

Introducing Apple Vision Pro, the new 15-inch MacBook Air with M2, Mac Studio with M2 Max and M2 Ultra, Mac Pro with M2 Ultra, and previews of iOS 17, iPadOS 17, macOS Sonoma, and watchOS 10.

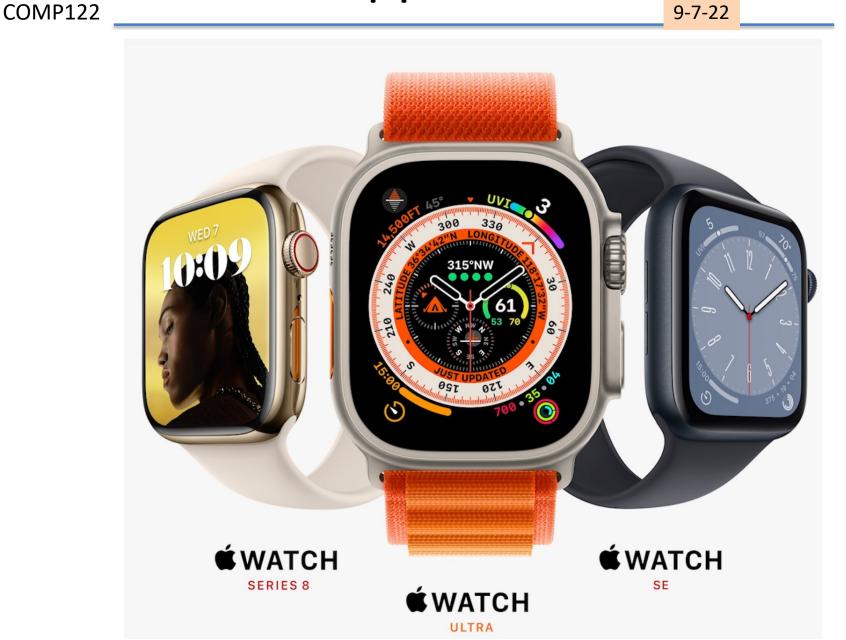

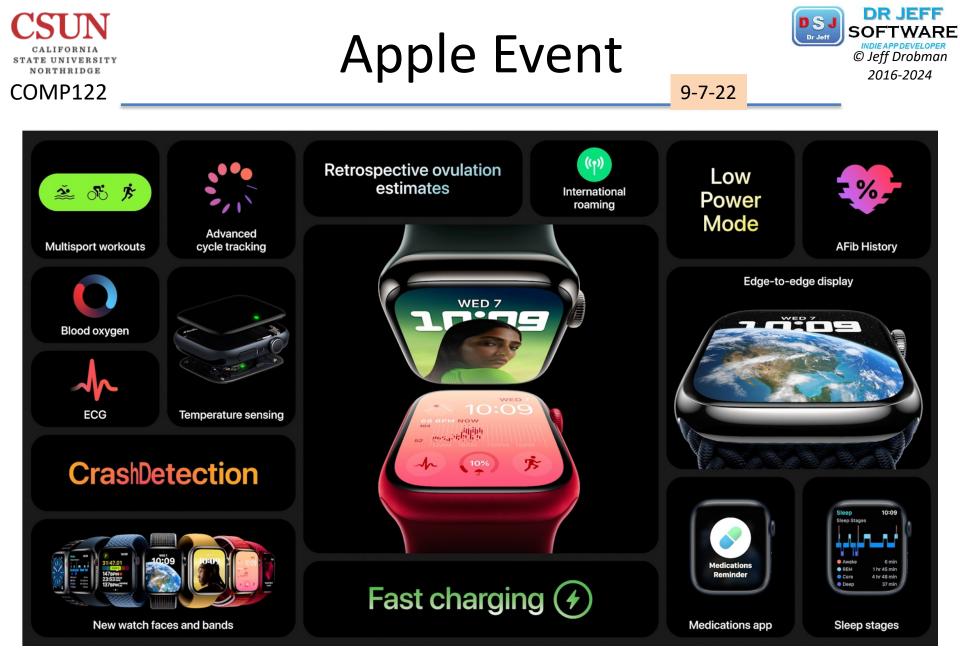

Apple Event September 7, 2022

Introducing an all-new iPhone lineup, rebuilt AirPods Pro, three new Apple Watch models, and an exciting update to Apple Fitness+.

**WWDC** June 6, 2022

Introducing the new MacBook Air, 13-inch MacBook Pro, iOS 16, iPadOS 16, macOS Ventura, and watchOS 9.

## Apple iPhone 15 Event

9-12-23

# Apple iPhone 15 Event

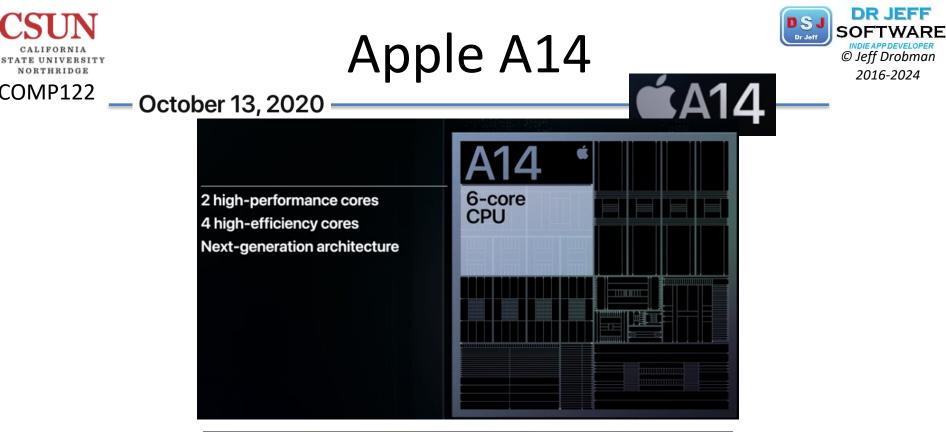

## 2 high-performance cores

NORTHRIDGE

**COMP122**

Up to 10% faster Improved branch prediction Wider decode & execution engines

## 4 high-efficiency cores

Most efficient mobile CPU 3x performance/watt vs. competition

## **2x faster Neural Engine**

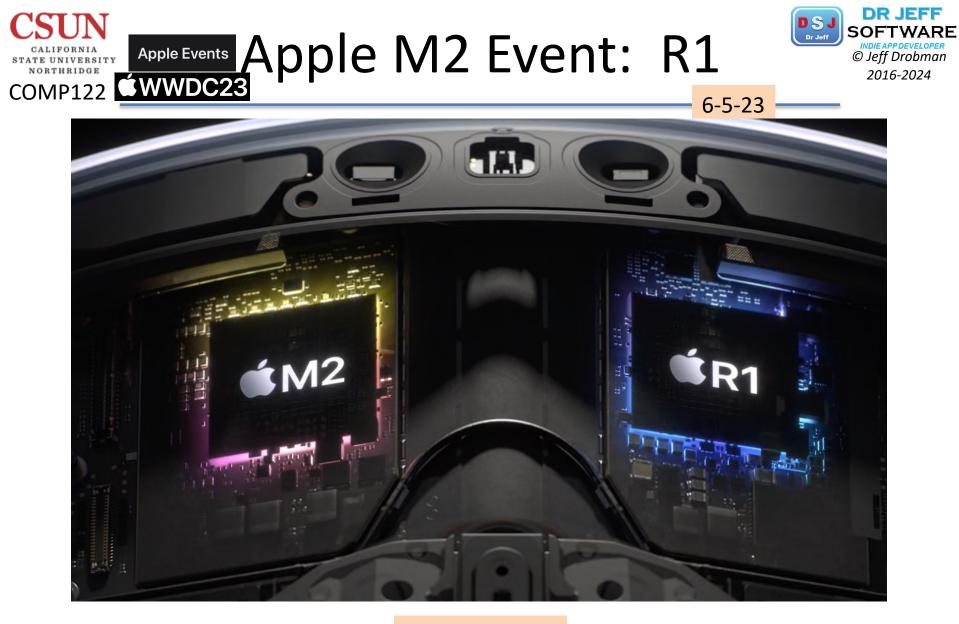

## Apple M2 Event

**Apple Events**

ORTHRIDGE

**COMP122**

6-5-23

# **ÚWWDC23**

Introducing Apple Vision Pro and the era of spatial computing. The new 15-inch MacBook Air with M2, Mac Studio with M2 Max and M2 Ultra, and Mac Pro with M2 Ultra. And previews of iOS 17, iPadOS 17, macOS Sonoma, and watchOS 10.

## **Vision Pro**

## Apple Event

NORTHRIDGE

**COMP122**

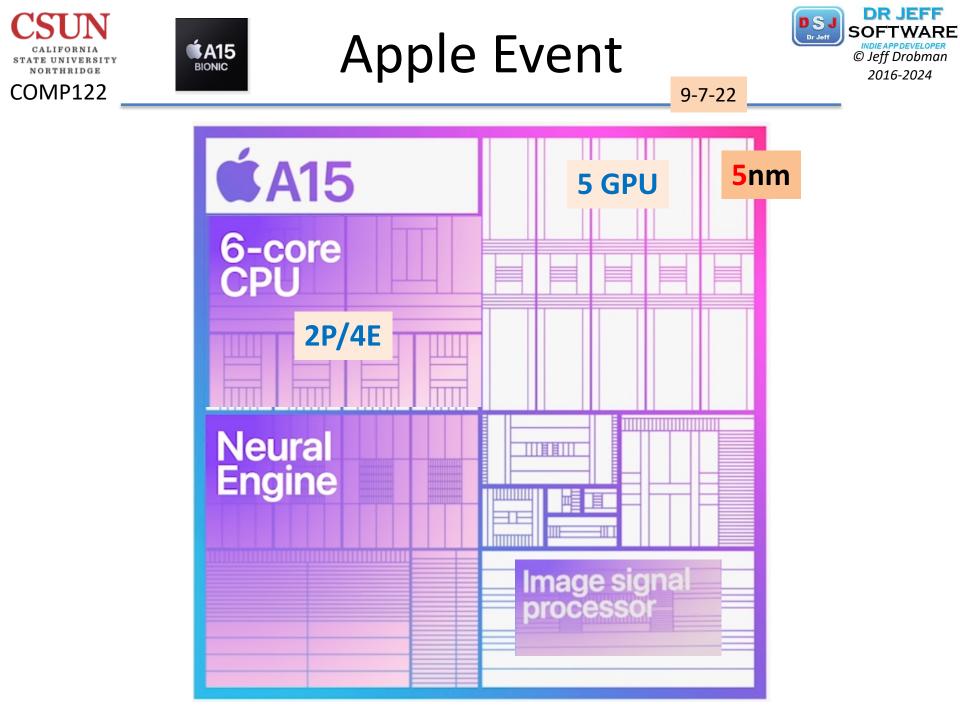

9-7-22

# Apple Events Fall 2022 **Apple Event** Watch on 9/7 at 10 a.m. PT. View online at apple.com or on the Apple TV app.

## **Apple Event**

Watch on 9/7 at 10 a.m. PT. View online at apple.com or on the Apple TV app.

## Apple Event

CALIFORNIA STATE UNIVERSITY NORTHRIDGE

introducing the new MacBook Air, 13-inch MacBook Pro, iOS 16, iPadOS 16, macOS Ventura, and watchOS 9.

## New Apple Event

NORTHRIDGE

**COMP122**

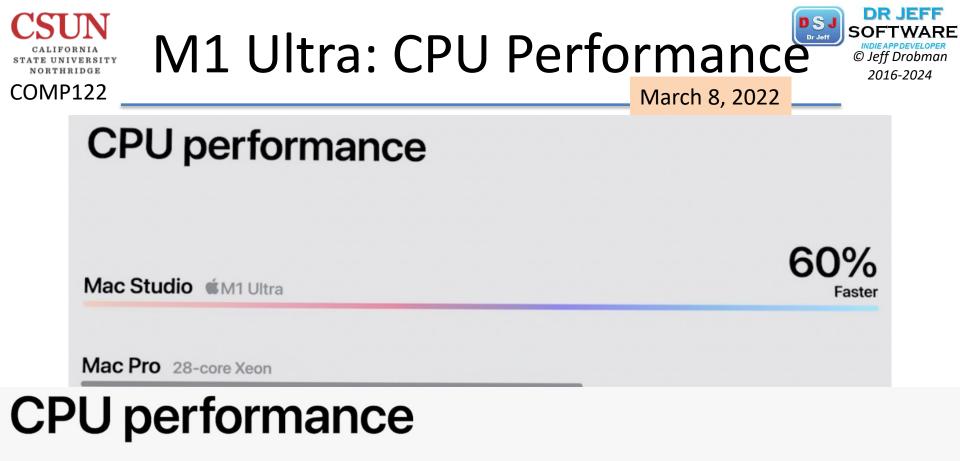

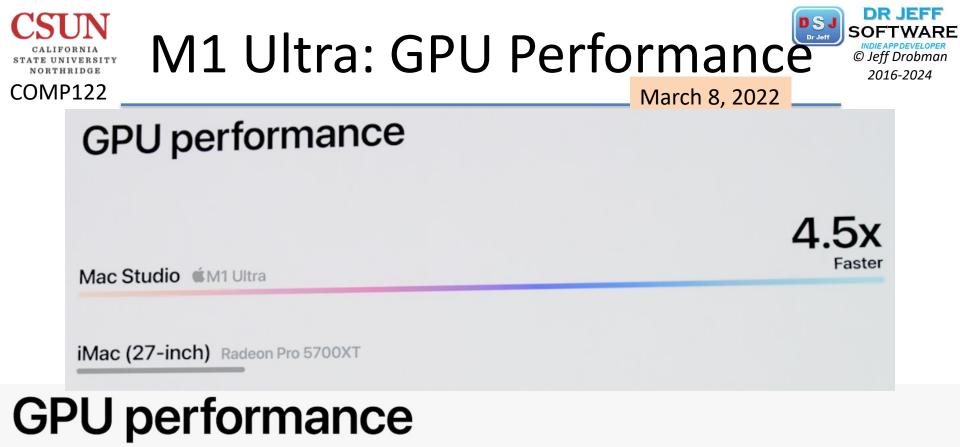

March 8, 2022

# Apple silicon Apple Event

Watch on 3/8 at 10 a.m. PST. View online at apple.com or on the Apple TV app.

ORTHRIDGE

**COMP122**

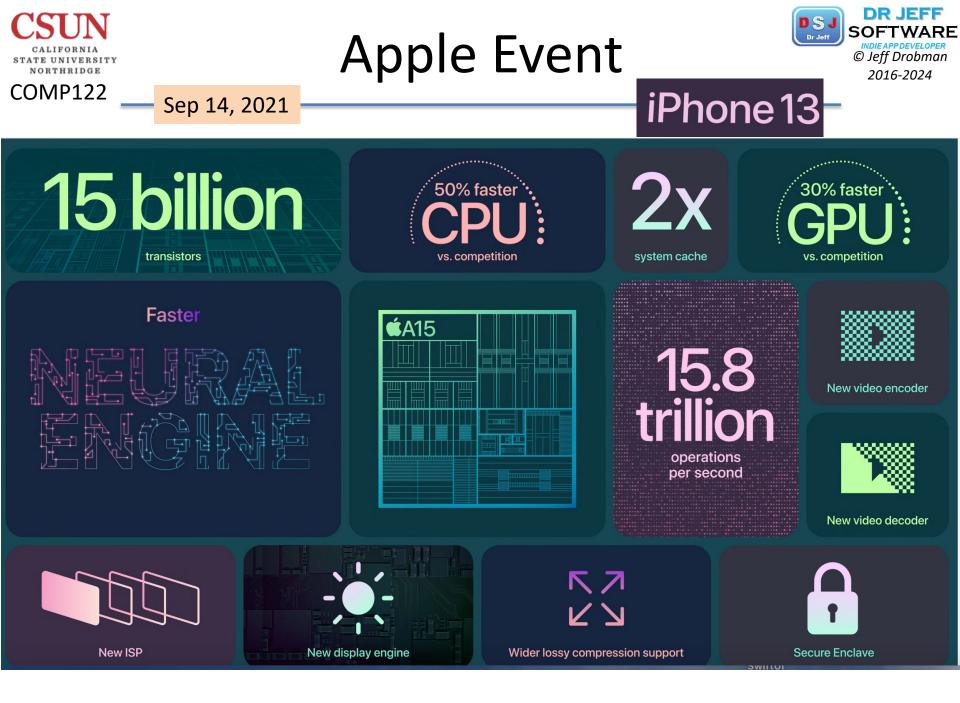

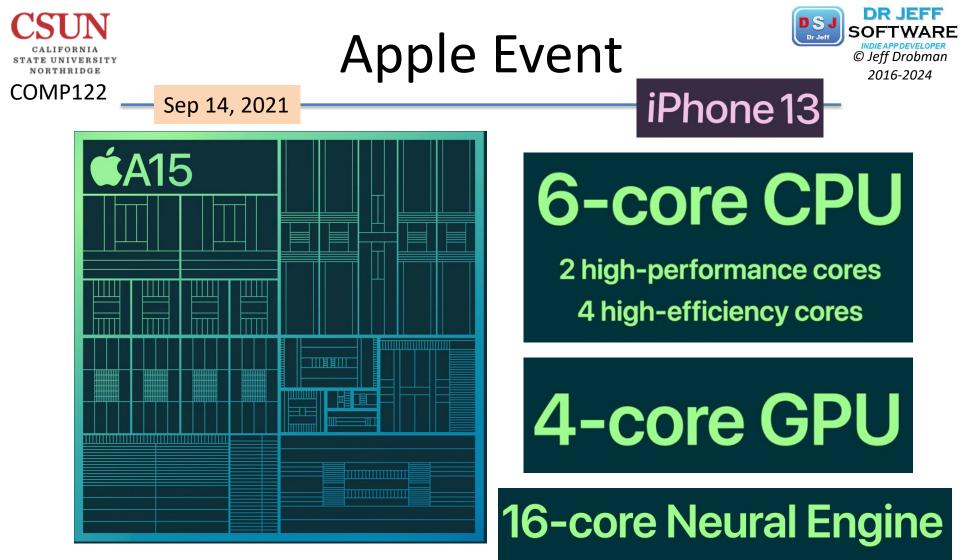

## iPhone13

# Now for the highlights.

Introducing iPhone 13 Pro, iPhone 13, Apple Watch Series 7, and the new iPad mini and iPad.

# Apple Buildings

CALIFORNIA STATE UNIVERSITY NORTHRIDGE

COMP122

## **Apple Buildings**

## - October 13, 2020 -

Section

Apple Phones

#### CSUN CALIFORNIA STATE UNIVERSITY NORTHRIDGE

# ARM Chips (SoC)

**COMP122**

#### Joe Zbiciak

Developed practical algorithms actually used in production.  $\cdot$  6mo

#### Who makes the ARM processor?

Quora

Just about everybody but ARM.

ARM develops the architecture, and develops its own RTL implementations. But outside of a handful of test chips, ARM does not manufacture any of the volume production ARM products out there.

I know of a few custom microarchitectures that implement the ARM ISA other than Apple.

- Qualcomm Krait 🖄 and Kryo 🖄

- Fujitsu A64FX ☑

- Cavium Vulcan

- Samsung Exynos M1 ☑ through M4 ☑

- Ampere Siryn. 🗗

- Marvell ThunderX3

Canceled)

- AppliedMicro Storm, ☑ Shadowcat, ☑ and Skylark ☑

All the production ARM processors come from:

- Apple

- Samsung

- Qualcomm

- Amazon

- Texas Instruments

- Microchip

- NXP / Freescale

- ST Microelectronics

- Broadcom

- Google

- Tesla

- ...and many more.

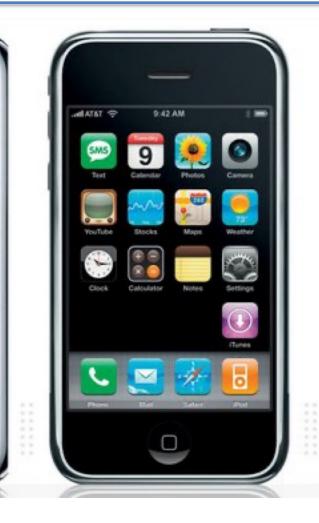

# iPhone

STATE UNIVERSITY NORTHRIDGE

**COMP122**

ANNOUNCED: Jan. 9, 2007

RELEASED: June 29, 2007

#### **KEY FEATURES:**

3.5-inch diagonal screen; 320 x 480 pixels at 163 ppi; 2-megapixel camera

PRICE: 4GB model, \$499; 8GB version, \$599 (with a two-year contract)

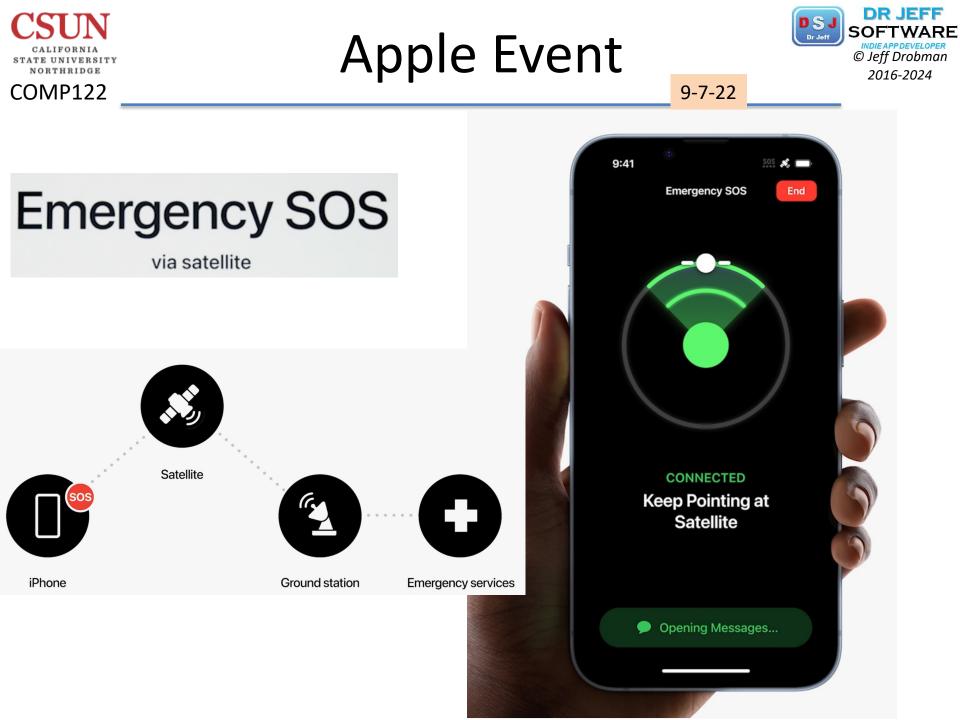

Apple Event: iPhone 14

9-7-22

### Apple Event

**COMP122**

JOBTHRIDGE

#### iPhone 14

Two great sizes: 6.1" and new, larger 6.7" Super Retina XDR displays.

Emergency SOS via satellite<sup>2</sup> and Crash Detection<sup>3</sup> for help when you need it most.

Advanced dual-camera system for more detailed, colorful shots. Sharper selfies.

Superspeedy A15 Bionic chip with 5-core GPU.

Our best battery life ever on iPhone 14 Plus. And all-day battery life on iPhone 14.4

Industry-leading durability features like Ceramic Shield and water resistance.<sup>6</sup>

Action mode takes smooth handheld videos when you're on the move.

5G cellular for superfast streaming, gaming, downloading, and more.<sup>5</sup>

Dynamic Island, a magical new way to interact with your iPhone.

Always-On display — the

info you want, at a glance.

| sos           |

|---------------|

| (sos)         |

| ( SOS )       |

| (SOS)         |

| ເວບວ          |

| 1000          |

|               |

|               |

| $\sim$ $\sim$ |

| $\sim$        |

|               |

Emergency SOS via satellite<sup>2</sup> and Crash Detection<sup>3</sup> for help when you need it most.

Pro camera system with 48MP Main camera. Four zoom options. Sharper selfies.

A16 Bionic — the ultimate smartphone chip.

9-7-22

iPhone 14 Pro

9:41

Amazing all-day battery life, even with so many new capabilities.<sup>4</sup>

Action mode takes smooth handheld videos when you're on the move.

5G cellular for superfast streaming, gaming, downloading, and more.<sup>5</sup>

### Apple Event

STATE UNIVERSITY NORTHRIDGE

**COMP122**

iPhone 12

5G

2x peak data rate

Camera (4)

Mag interface

Colors (5)

- October 13, 2020

Apple

2532 x 1170 2.8 million pixels 460 ppi

12MP Ultra Wide f/2.4 aperture 5-element lens 13 mm focal length 120° field of view

Section

Apple iPads

# Find the right iPad for you.

Compare iPad models >

iPad Pro The ultimate iPad experience.

From \$799

Available in October iPad Air Powerful. Colorful. Wonderful.

From \$599

New **iPad** Delightfully capable. Surprisingly affordable.

From \$329

iPad mini

Small in size. Big on capability.

From \$399

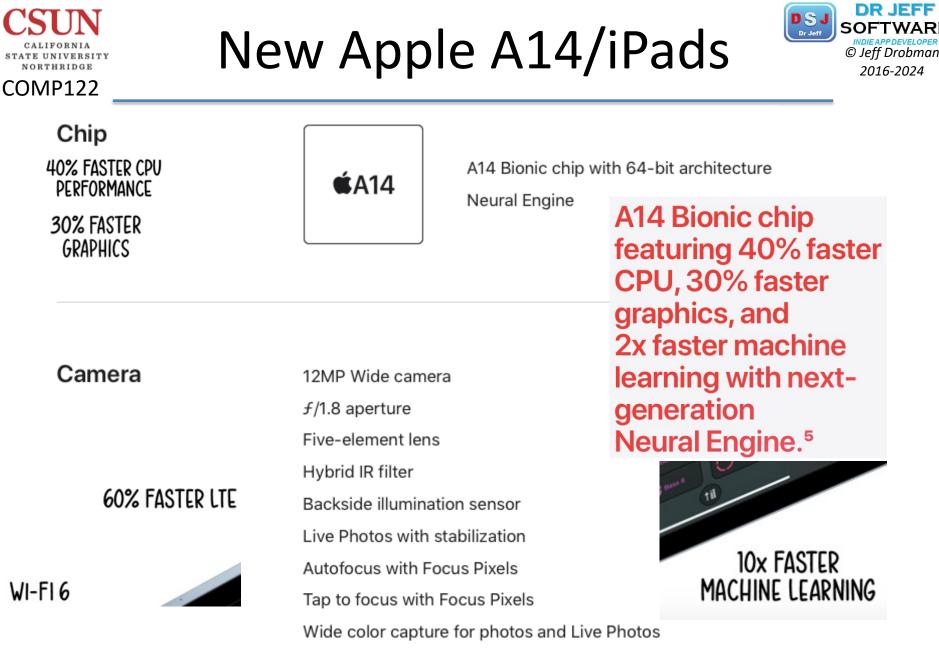

### New Apple A14/iPads

# tipad

The new iPad is more capable than ever. Now with the faster A12 Bionic chip, support or Apple Pencil, and the amazing features of iPadOS 14.

Available in October

iPad Air features an all-screen design with a 10.9-inch Liquid Retina display. The new A14 Bionic chip. And support for Apple Pencil and Magic Keyboard. Available in five finishes.

Panorama (up to 63MP)

Exposure control

### New Apple A14/iPads

Available in October

iPad Air

| Location |

|----------|

|----------|

| All models              |

|-------------------------|

| Digital compass         |

| Wi-Fi                   |

| iBeacon microlocation   |

|                         |

| Wi-Fi + Cellular models |

| Built-in GPS/GNSS       |

| Cellular                |

Touch ID integrated into the top button for fast, easy, and secure authentication.

#### Sensors

Touch ID Three-axis gyro Accelerometer Barometer Ambient light sensor

### Apple Mini

### — October 13, 2020 - Smart speaker/assistant

NORTHRIDGE

**COMP122**

Amazing sound Intelligent assistant Smart home Privacy and security

Section

# Apple Chips

A-series (ARM v8)

### Apple's ARM License

### Apple's ARM license is beyond architectural?

it look like Apple is allowed to add **proprietary ISA extensions** -- as long as they are ARM ISA compatible.

And apparently in Apple's case, they get to be a little bit incompatible (no **nVHE** mode, crazy **custom ISA extensions**, ...) Which is also obvious proof that they're their own designs, because literally nobody else could or would implement the same Appleproprietary ISA extensions. Here, we use some of the custom instructions in **m1n1**

Nope, you need to be compatible with the **architecture specification**, and it lays out exactly what can be implementation defined and what can't. E.g. you're allowed some freedom in what features to implement (Apple doesn't implement **EL3** and this is fine), and you can add implementation defined system **registers** (Apple has a huge number of them, e.g. to implement TSO for **Rosetta**). But you can't decide not to support **mandatory features** (Apple forces on **VHE mode**, which is not legal - VHE is optional, non-VHE mode isn't), nor can you add **extensions** to the core ISA. Apple added **AMX**, memory compression/decompression, a variant of the AT instructions that outputs to a GPR, and the whole **Guarded Execution** feature (two new parallel **exception levels** and machinery to call to/from them and lock down things to them), and possibly more, all of them in **reserved instruction encoding space**.

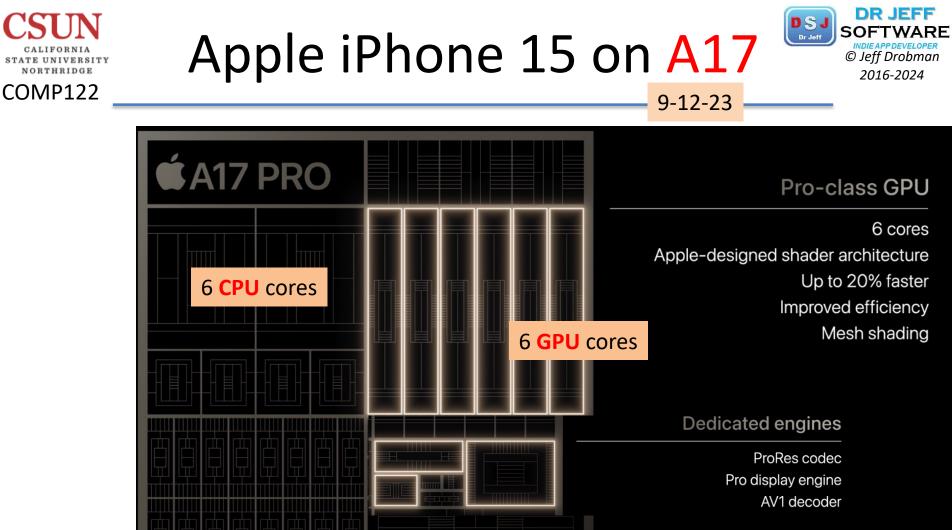

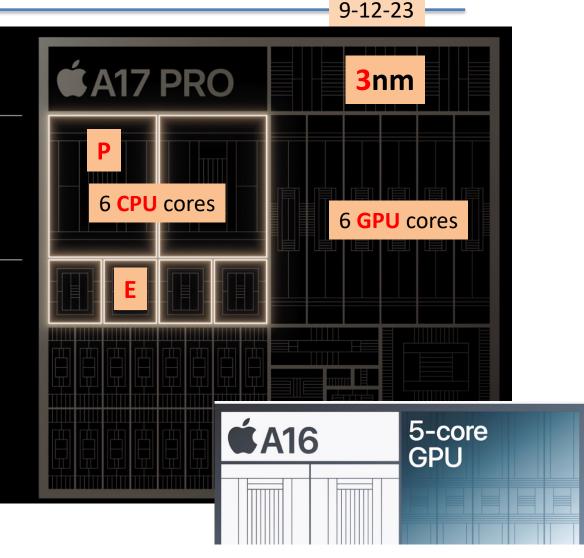

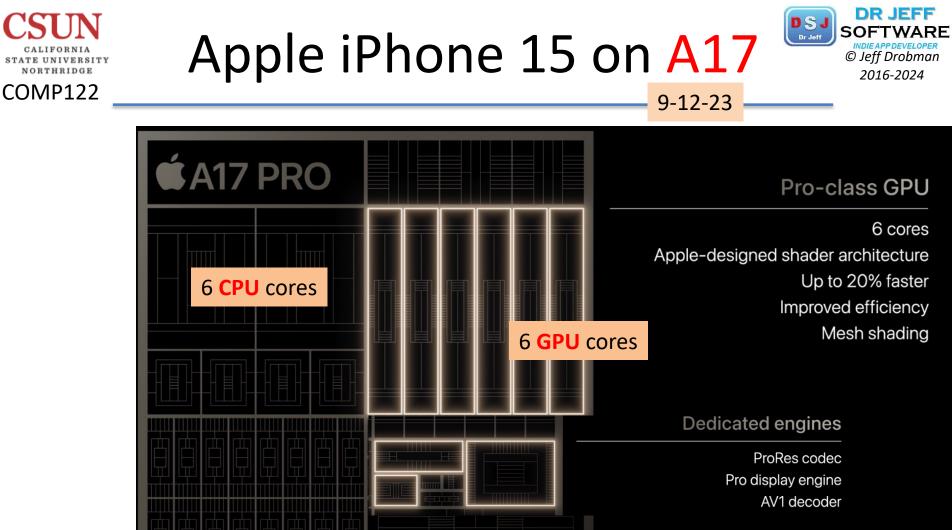

# Apple iPhone 15 on A17

#### 2 high-performance cores

NORTHRIDGE

**COMP122**

Up to 10% faster Improved branch prediction Wider decode & execution engines

#### 4 high-efficiency cores

Most efficient mobile CPU 3x performance/watt vs. competition

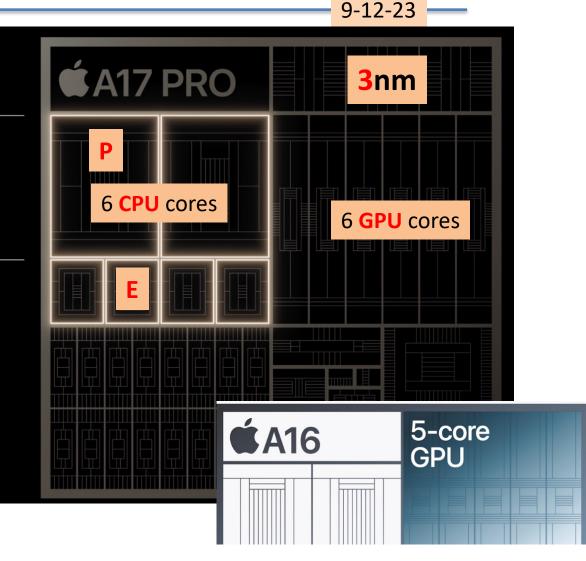

### New Apple A16

Why did Apple's mobile processor speed growth become slower compared to their early processor which usually doubled the performance compared to its previous generation?

#### Jeff Drobman

Lecturer at California State University, Northridge (2016-present) · Just now

the new A16 is the 1st Apple chip to use the latest 4nm process from TSMC. that allows more transistors on the same size die. but Apple chose to use the same number of CPU and GPU cores as for the A15 SoC, and instead uses the extra transistors for other functions like media and AI/ML. so we won't see much difference in benchmarked performance vs the A15. Apple shows a performance improvement vs their A13 chip.

### Apple Event

9-7-22

### **CPU performance**

A16 Bionic 2022

A13 Bionic 2019

Nearest competitor 2022

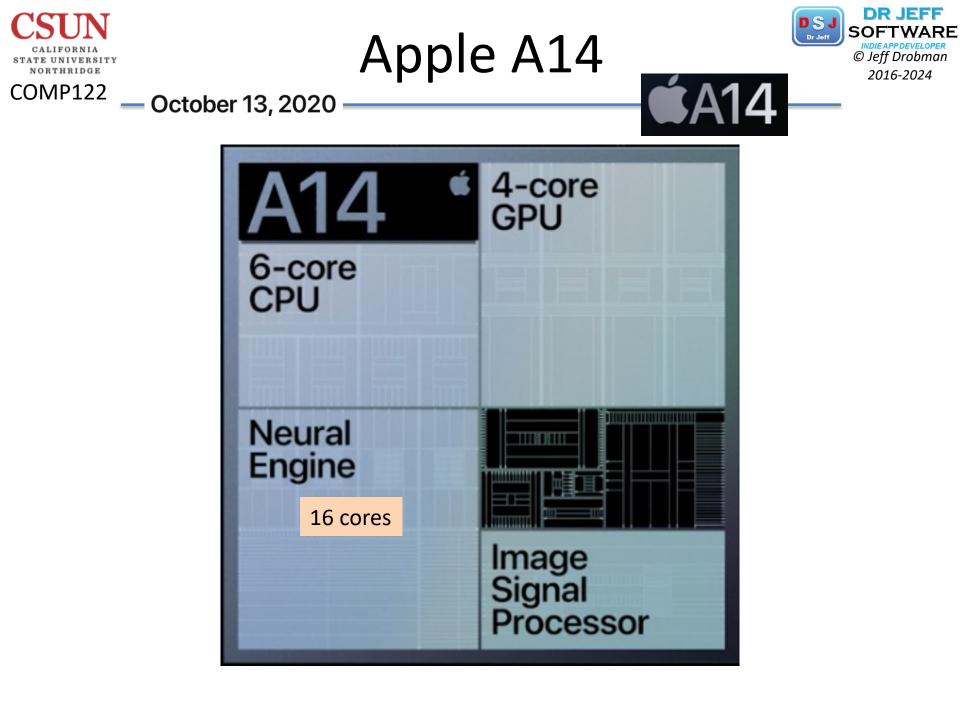

### New Apple A14/iPads

CALIFORNIA

NORTHRIDGE

**COMP122**

- October 13, 2020

# Apple A14

2nd-generation architecture 70% faster ML computations

| 16 cores   | Neural |

|------------|--------|

| 80% faster | Engine |

## Apple ARM SoC

#### Apple ARM SoC

the first ARM designs were for LOW POWER for portable devices. to achieve low power, the CPU was designed as simple RISC ISA and low clock frequency. Apple iPhones have used ARM from day 1, since they too initially didn't need high compute performance. over time, ARM models have evolved into more powerful models, including a 64-bit ISA -- necessary for today's computers. so now the time has come to start switching to ARM, mainly due to ARM being a licensable ISA and core that can be designed into anyone's SoC like Apple and many others do. I also note that the ARM ISA has evolved from a simple RISC to a more complex, CISC-like one.

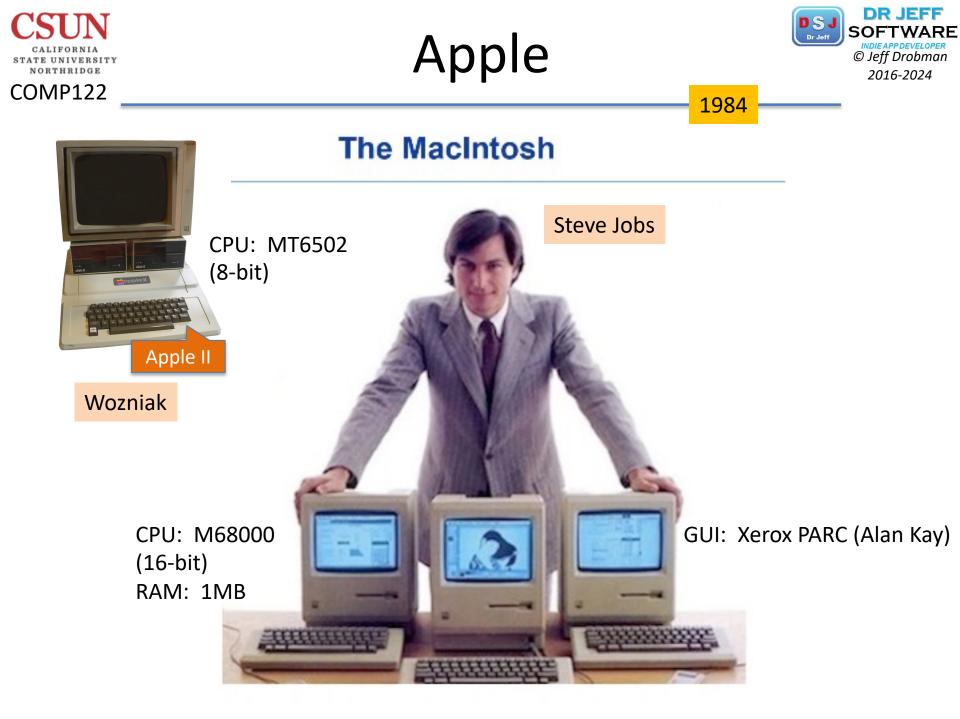

Apple has just announced they will replace x86 CPU's on their **Macs** with their own ARM-based **A13** (or next generation A14/15). makes sense for them to use their own chips now that they are powerful enough. this will also give Apple the same **AI** performance capabilities across all their hardware devices (e.g., Siri) -- way more AI power than any x86 chips.

The reason -- historically: Apple has upgraded their Macs for the same reason any company does: to be competitive they have to use a top performance CPU. so Apple switched from the 6502 (Apple II) to the M68000 in the 1st Mac, then upgraded to the Mot PPC. but then Mot stopped making PPC's, so Apple had nowhere else to go but x86 (Intel or AMD) – for Macs. note they have been making their own custom ARM-based chips (A series) for their phones.

Apple has long made their own chips with ARM CPU's since 2007 in their iPhones, designing an ever more powerful SoC (A4-A13). These new A13 SoC's are now much better than the Intel x86 chips in overall performance -- including machine learning (ML) via on-chip GPU cores plus neural engine -- and with superior power management.

### Apple A1-5

|      |           |                                                                                     |                             |                             |                     |         | 2007-1                                  | 0                                      |                                                                              |

|------|-----------|-------------------------------------------------------------------------------------|-----------------------------|-----------------------------|---------------------|---------|-----------------------------------------|----------------------------------------|------------------------------------------------------------------------------|

| Name | Model no. | Image                                                                               | Semiconductor<br>technology | Die size                    | Transistor<br>count | CPU ISA | CPU                                     | CPU cache                              | GPU                                                                          |

|      | APL0098   | (1)<br>33950030 ARM<br>8900B 07 19<br>N004BZ02<br>K4X16153PC-X6C3<br>• ECC45603 716 | 90 nm <sup>[9]</sup>        | 72 mm <sup>2[6]</sup>       |                     | ARMv6   | 412 MHz<br>single-core<br>ARM11         | L1i: 16 KB<br>L1d: 16 KB               | PowerVR MBX Lite @<br>103 MHz                                                |

|      | APL0278   | 33950048 ARM<br>X4X16323PD-R6C4<br>GMD050A3 831<br>APL0278A0<br>N18420A1 0834       | 65 nm <sup>[6]</sup>        | 36 mm <sup>2[6]</sup>       |                     | ARMv6   | 412–533 MHz<br>single-core<br>ARM11     | L1i: 16 KB<br>L1d: 16 KB               | PowerVR MBX Lite @<br>133 MHz                                                |

|      | APL0298   | 33950073ARM<br>K2132C2PD-50-F<br>ON0550908<br>APL0298<br>• NIPVNMPP 0919            | 65 nm <sup>[9]</sup>        | 71.8 mm <sup>2[19]</sup>    |                     | ARMv7   | 600 MHz<br>single-core<br>Cortex-A8     | L1i: 32 KB<br>L1d: 32 KB<br>L2: 256 KB | PowerVR SGX535                                                               |

|      | APL2298   | 33950075 ARM<br>8427030295-59028<br>94050295-59028<br>422298<br>M232R00 0948        | 45 nm <sup>[6]</sup>        | 41.6 mm <sup>2[6]</sup>     |                     | ARMv7   | 600–800 MHz<br>single-core<br>Cortex-A8 | L1i: 32 KB<br>L1d: 32 KB<br>L2: 256 KB | PowerVR SGX535 @<br>200 MHz                                                  |

| A4   | APL0398   | 1007 - 1007 - 1007 - 1007 - 1007                                                    | 45 nm <sup>[6][19]</sup>    | 53.3 mm <sup>2[6][19]</sup> |                     | ARMv7   | 0.8–1.0 GHz<br>single-core<br>Cortex-A8 | L1i: 32 KB<br>L1d: 32 KB<br>L2: 512 KB | PowerVR SGX535 <sup>[128]</sup>                                              |

|      | APL0498   | 0ELBBGEE BS+014Y                                                                    | 45 nm <sup>[38]</sup>       | 122.2 mm <sup>2[38]</sup>   |                     |         | 0.8–1.0 GHz<br>dual-core<br>Cortex-A9   | L1i: 32 KB<br>L1d: 32 KB<br>L2: 1 MB   | PowerVR SGX543MP2<br>(dual-core) @ 200 MH:<br>(12.8 GFLOPS) <sup>[129]</sup> |

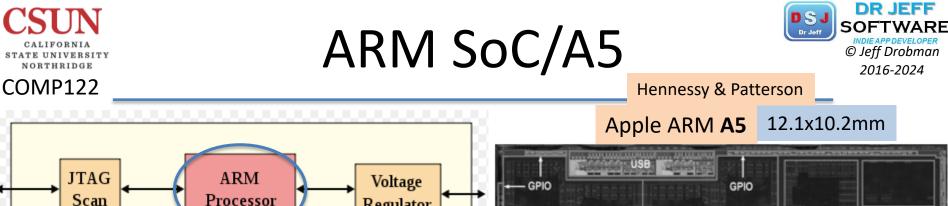

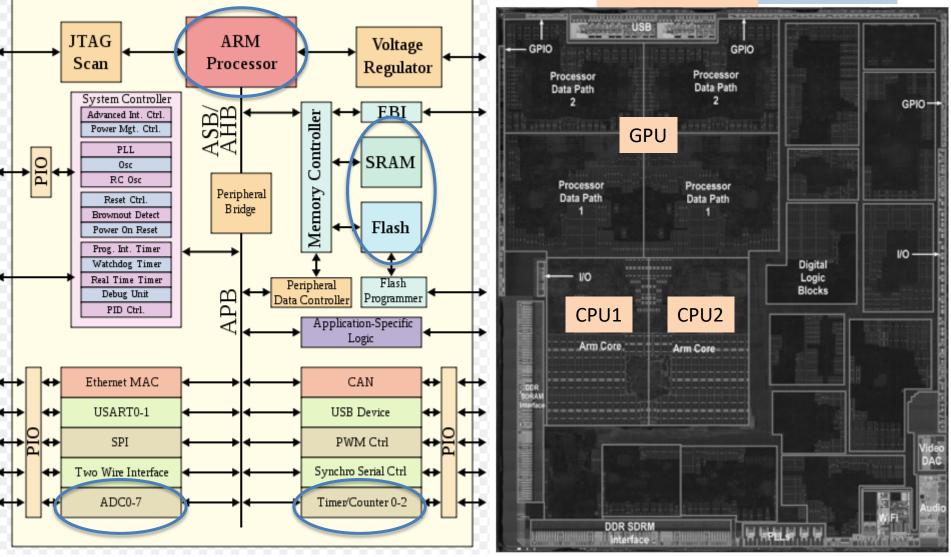

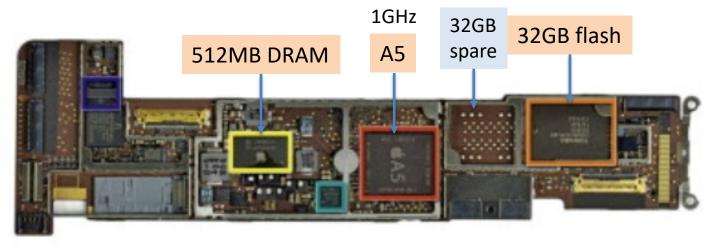

### A5 CPU on iPad2

JOBTHRIDGE

**COMP122**

#### Hennessy & Patterson —

The logic board of Apple iPad 2 in the previous figure. The photo highlights five integrated circuits. The large integrated circuit in the middle is the Apple A5 chip, which contains dual ARM processor cores that run at 1 GHz as well as 512 MB of main memory inside the package. The next figure shows a photograph of the processor chip inside the A5 package. The similar-sized chip to the left is the 32GB flash memory chip for non-volatile storage. There is an empty space between the two chips where a second flash chip can be installed to double storage capacity of the iPad. The chips to the right of the A5 include power controller and I/O controller chips. (Courtesy iFixit, www.ifixit.com)

### A Series: A4-7

The **Apple A4** is a 32-bit package on package (PoP) system on a chip (SoC) designed by Apple Inc. and manufactured by Samsung. It was the first SoC Apple designed in-house. The first product to feature the A4 was the first-generation iPad, followed by the iPhone 4, fourth-generation iPod Touch, and sec

#### 1<sup>st</sup> Apple design

✤ iPad 1✤ iPhone 4

#### iPhone 5S

32/64-bit

The **Apple A5** is a 32-bit system on a chip (SoC) designed by Apple Inc. and manufactured by Samsung. The first product Apple featured an A5 in was the iPad 2. Apple claimed during their media event on March 2, 2011 that the ARM Cortex-A9 central processing unit (CPU) in the A

iPad 2

The **Apple A7** is a 64-bit system on a chip (SoC) designed by Apple Inc. It first appeared in the iPhone 5S, which was announced on September 10, 2013, and the iPad Air, announced October 22, 2013. Apple states that it is up to twice as fast and has up to twice the graphics power compared

#### 64-bit

The **Apple A8** is a 64-bit ARMbased system on a chip (SoC) designed by Apple Inc. It first appeared in the iPhone 6 and iPhone 6 Plus, which were introduced on September 9, 2014. Apple states that it has 25% more CPU performance and 50% more graphics performance while

iPhone 6

The **Apple A10 Fusion** is a 64-bit ARM-based system on a chip (SoC), designed by Apple Inc. and manufactured by TSMC. It first appeared in the iPhone 7 and 7 Plus which were introduced on September 7, 2016, and is used in the sixth-generation iPad, seventh-generation iPad, and

iPhone 7

÷

÷Ö

#### iPhone 6S

The **Apple A9** is a 64-bit ARMbased system-on-chip (SoC), designed by Apple Inc. Manufactured for Apple by both TSMC and Samsung, it first appeared in the iPhone 6S and 6S Plus which were introduced on September 9, 2015. Apple states that it has 70% more CPU

#### iPhone 8

The **Apple A11 Bionic** is a 64-bit ARM-based system on a chip (SoC), designed by Apple Inc. and manufactured by TSMC. It first appeared in the iPhone 8, iPhone 8 Plus, and iPhone X which were introduced on September 12, 2017. Apple states that the two high-performance cores are 2.

#### A12-14 + M1

#### 64-bit

The **Apple A12 Bionic** is a 64-bit ARM-based system on a chip (SoC) designed by Apple Inc. It first appeared in the iPhone XS, XS Max, XR, the 2019 versions of the iPad Air and iPad Mini, and the iPad (2020). Apple states that the two high-performance cores are 15% faster and 50% more energy-ef

iPad Air/MiniiPhone XS

The **Apple A13 Bionic** is a 64-bit ARM-based system on a chip (SoC), designed by Apple Inc. It appears in the iPhone 11, 11 Pro/Pro Max and the iPhone SE. Apple states that the two high performance cores are 20% faster with 30% lower power consumption than the Apple

iPhone 11 8.5B Tx

#### ✤ iPhone 12 11.8B Tx

Ö

The **Apple A14 Bionic** is a 64-bit ARM-based System on a Chip (SoC), designed by Apple Inc. It appears in the fourth generation iPad Air, as well as iPhone 12 Mini, iPhone 12, iPhone 12 Pro, and iPhone 12 Pro Max. Apple states that the Central Processing Unit (CPU) performs up to 40%

#### MacBook Air/Pro 16B Tx

ø

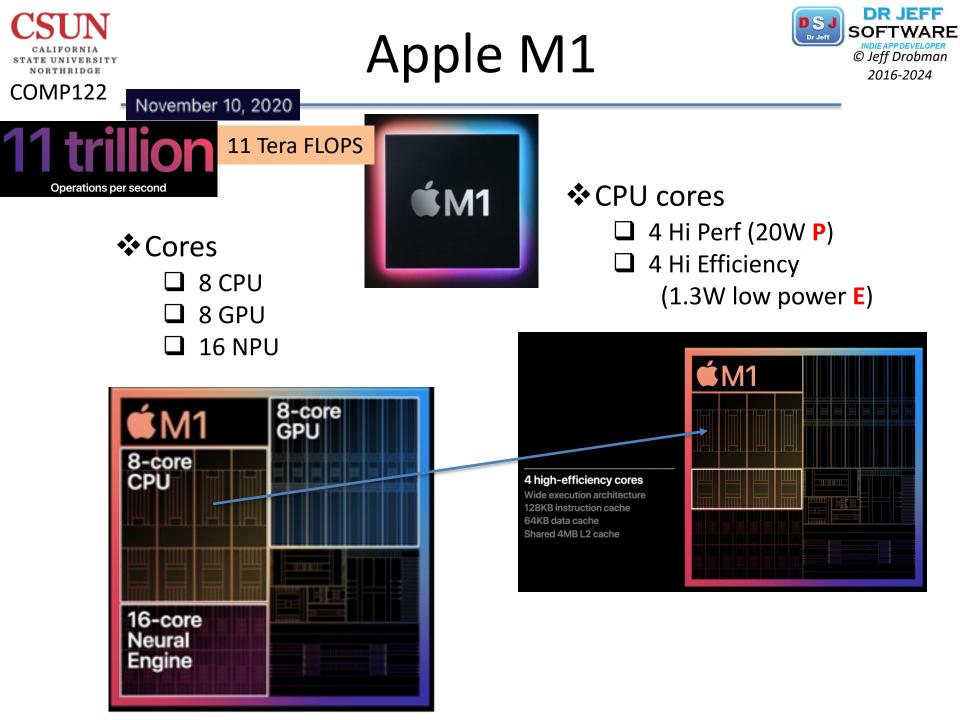

The **Apple M1** is the first ARMbased system on a chip (SoC) designed by Apple Inc. as a central processing unit (CPU) for its line of Macintosh computers. It is deployed in the MacBook Air, Mac mini, and the MacBook Pro. It is the first personal computer chip built using a 5 nm process. Ap

### Apple A13

### Apple A13

iPhone12,3

CALIFORNIA STATE UNIVERSITY NORTHRIDGE

COMP122

| Single-Core Score               | Multi-Core Score           |

|---------------------------------|----------------------------|

| 5472                            | 13769                      |

| Seekbench 4.4.1 for iOS AArch64 |                            |

| Result Information              |                            |

| Upload Date                     | September 11 2019 11:03 PM |

| Views                           | 3591                       |

| System Information              |                            |

| System Information              |                            |

| Operating System                | IOS 13.0                   |

| Model                           | iPhone12,3                 |

| Motherboard                     | D421AP                     |

| Memory                          | 3759 MB                    |

| Processor Information           |                            |

| Name                            | ARM                        |

| Topology                        | 1 Processor, 6 Cores       |

| Identifier                      | ARM                        |

| Base Frequency                  | 2.66 GHz                   |

| L1 Instruction Cache            | 48.0 KB x 1                |

| L1 Data Cache                   | 48.0 KB x 1                |

| L2 Cache                        | 4.00 MB x 1                |

# **Apple ARM A Series**

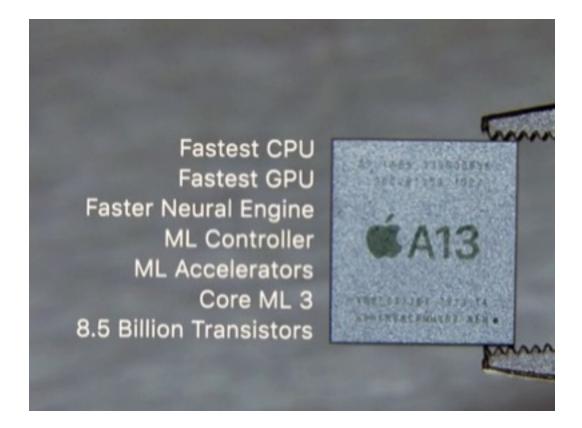

According to Apple, the chip is capable of performing one trillion operations per second and with an eight-core neural engine, A13 Bionic chip has the most Machine Learning performance that adds 6x faster matrix multiplication.

Quora post

This time Apple has focused mainly on machine learning and the A13 Bionic has Fastest CPU and GPU in a Smartphone.

Qualcomm Snapdragon 800 Series flagship is the biggest competitor of Apple. Qualcomm has its Snapdragon 855 and 855 Plus flagship SoC but the successor to Snapdragon 855 is yet to get announced were Apple has already unveiled A13 Bionic.

The Apple A13 Bionic is fabricated on TSMC 2nd (EUV Lithography Process) Generation 7nm process and Snapdragon 855 and 855 Plus Both are fabricated on TSMC 7nm DUV process. And A13 has over 8.3 Billion Transistors and that of 855 Snapdragon has 6.9 Billion Transistors.

Image source: A12X Bionic - Apple - WikiChip 🖉

#### COMP122

# Apple A11/12/13

| Name           | Model no. | Image                                                                                                         | Semiconductor<br>technology | Die size                   | Transistor<br>count | CPU ISA                    | CPU                                                                   | CPU cache                                                                  | GPU                             |

|----------------|-----------|---------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------|---------------------|----------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------|

| A13<br>Bionic  | APL1W85   | APL 1998 339500488<br>1942050096 1932<br>CALOSODE 1932<br>CALOSODE 1932<br>HE073 94 H 1914<br>KEBASHEGAM 1901 | 7 nm FinFET<br>(TSMC N7P)   | 98.48 mm <sup>2[174]</sup> | 8.5 billion         | ARMv8.4-A <sup>[175]</sup> | 2.65 GHz<br>hexa-core (2×<br>Lightning + 4×<br>Thunder)               | L1i: 128 KB<br>L1d: 128 KB<br>L2: 8 MB<br>L3: <i>none</i> <sup>[176]</sup> | Custom design (quad-<br>core)   |

| A12Z<br>Bionic | APL1083   | 1083                                                                                                          | 7 nm FinFET<br>(TSMC N7)    | ≈135 mm <sup>2[172]</sup>  | 10 billion          | ARMv8.3-A <sup>[168]</sup> | 2.49 GHz octa-<br>core (4× Vortex<br>+ 4× Tempest)                    | L1d: 128 KB<br>L2: 8 MB<br>L3: <i>none</i> <sup>[173]</sup>                | Custom design (octa-<br>core)   |

| A12X<br>Bionic |           |                                                                                                               |                             |                            |                     |                            |                                                                       | L1i: 128 KB                                                                | Custom design (hepta-<br>core)  |

| A12<br>Bionic  | APL1W81   | • • • • • • • • • • • • • • • • • • •                                                                         | 7 nm FinFET<br>(TSMC N7)    | 83.27 mm <sup>2[167]</sup> | 6.9 billion         | ARMv8.3-A <sup>[168]</sup> | 2.49 GHz<br>hexa-core (2×<br>Vortex + 4×<br>Tempest) <sup>[169]</sup> | L1i: 128 KB<br>L1d: 128 KB<br>L2: 8 MB<br>L3: <i>none</i> <sup>[169]</sup> | Custom design (quad-<br>core)   |

| A11<br>Bionic  | APL1W72   | • mann 1000                                                                                                   | 10 nm FinFET<br>(TSMC)      | 87.66 mm <sup>2[162]</sup> | 4.3 billion         | ARMv8.2-A <sup>[163]</sup> | 2.39 GHz<br>hexa-core (2×<br>Monsoon + 4×<br>Mistral)                 | L1i: 64 KB<br>L1d: 64 KB<br>L2: 8 MB<br>L3: <i>none</i> <sup>[164]</sup>   | Custom design (triple-<br>core) |

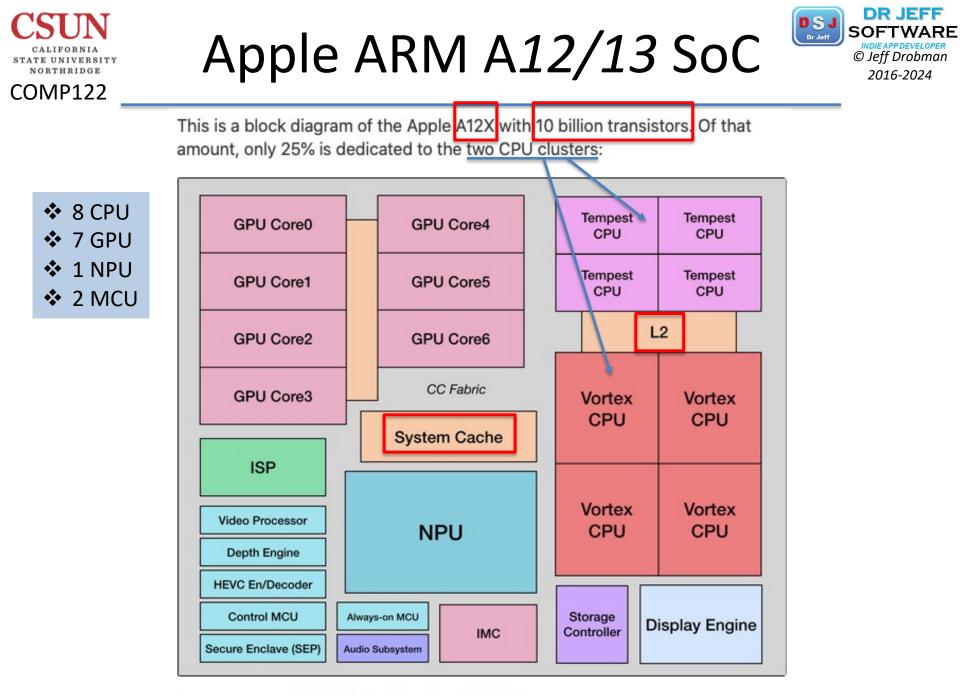

#### Apple A12X Bionic

CALIFORNIA STATE UNIVERSITY NORTHRIDGE

COMP122

| LaunchedOctober 30, 2018DiscontinuedMarch 18, 2020Designed byApple Inc.CommonTSMC <sup>[1]</sup> manufacturer(s)TSMC <sup>[1]</sup> Product codeAPL1083 <sup>[2]</sup> Max. CPU clockto 2.49 <sup>[3]</sup> GHzrateCacheL1 cache128 KB instruction, 128 KB<br>dataL2 cache8 MBArchitectterand classificationApplicationMobileMin. feature size7 nm <sup>[4]</sup> | General Info                    |                            |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------------|--|--|--|--|--|--|

| Designed byApple Inc.CommonTSMC <sup>[1]</sup> manufacturer(s)APL1083 <sup>[2]</sup> Product codeAPL1083 <sup>[2]</sup> Max. CPU clockto 2.49 <sup>[3]</sup> GHzrateCacheL1 cache128 KB instruction, 128 KB<br>dataL2 cache8 MBArchitectter and classificationApplicationMobile                                                                                   | Launched                        | October 30, 2018           |  |  |  |  |  |  |

| Common<br>manufacturer(s)TSMC[1]Product codeAPL1083[2]Max. CPU clockto 2.49[3] GHzrateCacheL1 cache128 KB instruction, 128 KB<br>dataL2 cache8 MBArchitecture and classificationApplicationMobile                                                                                                                                                                 | Discontinued                    | March 18, 2020             |  |  |  |  |  |  |

| manufacturer(s)Product codeAPL1083 <sup>[2]</sup> Max. CPU clockto 2.49 <sup>[3]</sup> GHzrateCacheL1 cache128 KB instruction, 128 KB<br>dataL2 cache8 MBArchitecture and classificationApplicationMobile                                                                                                                                                         | Designed by                     | Apple Inc.                 |  |  |  |  |  |  |

| Max. CPU clock<br>rateto 2.49 <sup>[3]</sup> GHzCacheL1 cache128 KB instruction, 128 KB<br>dataL2 cache8 MBArchitecture and classificationApplicationMobile                                                                                                                                                                                                       |                                 | TSMC <sup>[1]</sup>        |  |  |  |  |  |  |

| rate Cache L1 cache 128 KB instruction, 128 KB data L2 cache 8 MB Architecture and classification Application Mobile                                                                                                                                                                                                                                              | Product code                    | APL1083 <sup>[2]</sup>     |  |  |  |  |  |  |

| L1 cache 128 KB instruction, 128 KB<br>data<br>L2 cache 8 MB<br>Architecture and classification<br>Application Mobile                                                                                                                                                                                                                                             |                                 | to 2.49 <sup>[3]</sup> GHz |  |  |  |  |  |  |

| data<br>L2 cache 8 MB<br>Architecture and classification<br>Application Mobile                                                                                                                                                                                                                                                                                    |                                 | Cache                      |  |  |  |  |  |  |

| Architecture and classification<br>Application Mobile                                                                                                                                                                                                                                                                                                             | L1 cache                        |                            |  |  |  |  |  |  |

| Application Mobile                                                                                                                                                                                                                                                                                                                                                | L2 cache                        | 8 MB                       |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                   | Architecture and classification |                            |  |  |  |  |  |  |

| Min. feature size 7 nm <sup>[4]</sup>                                                                                                                                                                                                                                                                                                                             | Application                     | Mobile                     |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                   | Min. feature size               | 7 nm <sup>[4]</sup>        |  |  |  |  |  |  |

noral Info

## Apple A12X

#### Design [edit]

The A12X features an Apple-designed 64-bit ARMv8.3-A octa-core CPU, with four high-performance cores called **Vortex** and four energy-efficient cores called **Tempest**.<sup>[4][1]</sup> The Vortex cores are a 7-wide decode out-of-order superscalar design, while the Tempest cores are a 3-wide decode out-of-order superscalar design. Like the Mistral cores, the Tempest cores are based on Apple's Swift cores from the Apple A6, and are similar in performance to ARM Cortex-A73 CPU cores.<sup>[5][6]</sup> It is Apple's first SoC with an octa core CPU.<sup>[1]</sup>

The A12X integrates an Apple-designed septa core graphics processing unit (GPU) with twice the graphics performance of the A10X.<sup>[4]</sup> Embedded in the A12X is the M12 motion coprocessor.<sup>[7]</sup> The A12X includes dedicated neural network hardware that Apple calls a "Next-generation Neural Engine".<sup>[4]</sup> This neural network hardware, which is the same as found in the A12,<sup>[1]</sup> can perform up to 5 trillion operations per second.<sup>[4]</sup>

The A12X is manufactured by TSMC using a 7 nm FinFET process, and it contains 10 billion transistors<sup>[1][4]</sup> vs. the 6.9 billion on the A12.<sup>[8]</sup> The A12X is paired with 4 GB of LPDDR4X memory in the third-generation 12.9" iPad Pro and the 11" iPad Pro or 6 GB in the 1TB storage configurations.<sup>[9][2]</sup>

#### Products that include the Apple A12X [edit]

- iPad Pro 2018 11-inch (First-generation)

- iPad Pro 2018 12.9-inch (Third-generation)

# Apple ARM A13

Intel chips are **x86** ISA and multi-core CPU (only). Apple chips are **ARM** ISA with multi-core CPU's, GPU's, and NPU, MCU's. The latest Apple chip is the **A13**, succeeding the powerful **A12X** as the first "bionic" SoC.

**A13**: The A13 is the latest multi-core architecture designed by Apple with 8.5B transistors manufactured at TSMC (7nm EUV) -- extremely state-of-the-art. The A13 was released Sept. **2019** and is used in the iPhone **11**.

It contains a large number of **ARMv8** ISA cores: 6 CPU (2.65GHz) + 4 GPU + 8 NPU + 2 MCU. (Note that the A12X/Z has 8 CPU cores + 8 GPU's). All cores are Apple designed (ARM 64-bit v8 ISA is licensed). It includes a Neural engine (8x NPU) with machine learning (core ML 3 at 6x faster matrix multiply) -- which sets it apart from Intel chips without GPU's or an NPU. The GPU's can perform 1 trillion operations per second (1 Tflops=1000 Gflops), and the NPU may hit 5 Tflops. It has extreme power management as well (so good for portables and mobile).

Apple ARM A12/13 SoC

Spaces

Q Sea

2

Notifications

Home

Quora

Matthew J. Stott, Senior Systems & Mac Engineer (1996-present) Answered Sep 30

Answer

It's called a SoC - System on Chip. It means the CPU package includes a lot more than just the CPU cores. What's changed with the A13 is even more power management abilities to shut off unused parts of the A13 but also right down to individual transistors as well. It is the most advanced power management in use right now. It is responsible for the excellent battery life of the 11, 11 Pro, 11 Pro Max iPhones. Yes, they increased the battery capacity a bit at the same time but that is just improved battery engineering.

Add to Yowan's A12X the Image Processing Core, a couple of Machine Learning accelerator cores and a bit less on the GPU with the A13 Bionic SoC. It is expected there will be an A13X for upgrade iPad Pros coming soon.

# Apple A13

Quora post

And I think iPhones are going to be more power-efficient than Snapdragon 855 powered Android Phones. If you are asking about CPU, then the A13 Bionic is based on 64-bit Fusion Architecture. It is a Hexa-Core CPU with 2 Performance cores and 4 Efficiency cores. And it consumes 40% less power than the A12 Bionic. Coming to 855 Snapdragon, both Snapdragon 855 and 855 Plus is an ARM 64-bit SoC with Kryo 485 Octa-Core CPU. And it has Three CPU Clusters: 1 Cortex-A76 Prime Core, 3 Cortex-A76 Performance Cores and 4 Cortex-A55 Efficiency Cores. From these it seems Snapdragon 855 will definitely be a strong competitor for the Apple A13 Bionic Chip.

Moreover, while talking about GPU, for Apple, it is an Apple-designed Quad Core GPU and Snapdragon 855 has Adreno 640 GPU. And I don't think the Snapdragon will beat the performance of Apple's A13 bionic chip.

(A

#### A Series: ARMv7/8

|               | ISA       |                                          | Cores                                                                                                                                                                         |                         | Cache                       |              | Spe    | ed    |

|---------------|-----------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------------|--------------|--------|-------|

| Ax<br>(Apple) | ARMv7-A   | Swift <sup>[73]</sup>                    | 2 cores. ARM / Thumb / Thumb-2 / DSP / SIMD / VFPv4 FPU<br>/ NEON                                                                                                             | L1: 32 KB               | 3.5 DMIP<br>per co          |              |        |       |

|               | ARMv8-A   | Cyclone <sup>[74]</sup>                  | 2 cores. ARM / Thumb / Thumb-2 / DSP / SIMD / VFPv4 FPU<br>/ NEON / TrustZone / AArch64. Out-of-order, superscalar.                                                           | L1: 64 KB / 64          | 1.3 or 1.4                  | 4 GHz        |        |       |

|               | ARMv8-A   | Typhoon <sup>[74][75]</sup>              | 2 or 3 cores. ARM / Thumb / Thumb-2 / DSP / SIMD / VFPv4<br>FPU / NEON / TrustZone / AArch64                                                                                  |                         |                             |              |        | 5 GHz |

|               | ARMv8-A   | Twister <sup>[76]</sup>                  | 2 cores. ARM / Thumb / Thumb-2 / DSP / SIMD / VFPv4 FPU<br>/ NEON / TrustZone / AArch64                                                                                       | L1: 64 KB / 64 K        | 1.85 or 2.2                 | 26 GHz       |        |       |

|               | ARMv8.1-A | Hurricane and<br>Zephyr <sup>[77]</sup>  | Hurricane: 2 or 3 cores. AArch64, 6-decode, 6-issue, 9-wide,<br>superscalar, out-of-order<br>Zephyr: 2 or 3 cores. AArch64.                                                   | L1: 64 KB / 64 K<br>4 N | B, L2: 3 MB o<br>MB or 0 MB | 2.34 or 2.3  | 38 GHz |       |

|               | ARMv8.2-A | Monsoon and<br>Mistral <sup>[78]</sup>   | Monsoon: 2 cores. AArch64, 7-decode, ?-issue, 11-wide,<br>superscalar, out-of-order<br>Mistral: 4 cores. AArch64, out-of-order, superscalar. Based<br>on Swift.               | L1I: 128 KB, L1         | 2.39 G                      | àHz          |        |       |

|               | ARMv8.3-A | Vortex and<br>Tempest <sup>[79]</sup>    | Vortex: 2 or 4 cores. AArch64, 7-decode, ?-issue, 11-wide,<br>superscalar, out-of-order<br>Tempest: 4 cores. AArch64, 3-decode, out-of-order,<br>superscalar. Based on Swift. | code, out-of-order,     |                             |              | 2.5 G  | Hz    |

|               | ARMv8.4-A | Lightning and<br>Thunder <sup>[80]</sup> | Lightning: 2 cores. AArch64, 7-decode, ?-issue, 11-wide,<br>superscalar, out-of-order<br>Thunder: 4 cores. AArch64, out-of-order, superscalar.                                | L1: 128 KB / 128        | KB, L2: 8 ME                | 3, L3: 16 MB | 2.66 G | àHz   |

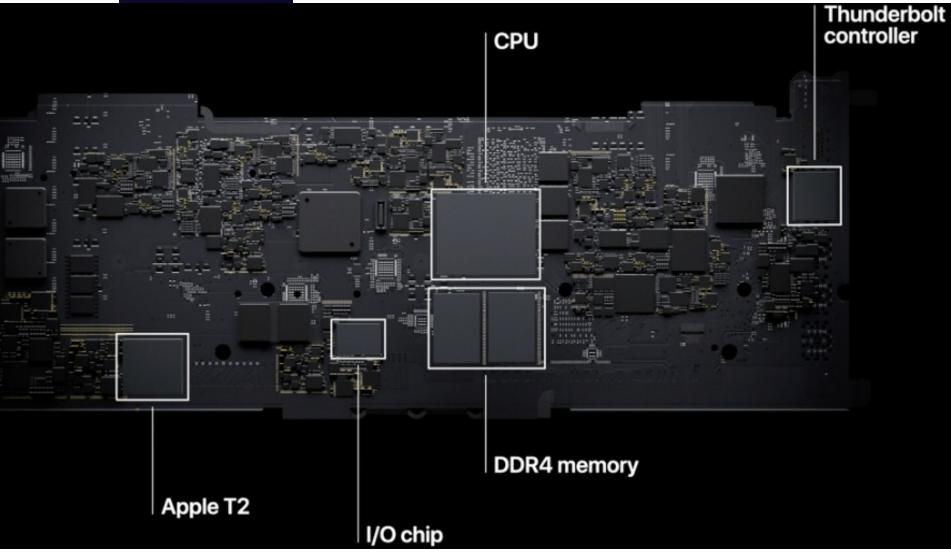

# Apple T1/2 SoC

#### MacBook Pro

#### T series list [edit]

| Name | Model no.                | Image                | Semiconductor<br>technology | Die<br>size | CPU<br>ISA  | CPU | CPU<br>cache | GPU | Memory<br>technology | Introduced       | Utilizing devices                                                                                                                                                                                                                                                                                                                                                   |

|------|--------------------------|----------------------|-----------------------------|-------------|-------------|-----|--------------|-----|----------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T1   | APL1023 <sup>[190]</sup> | • 2610038776 62011d¥ |                             |             | ARMv7       |     |              | TBD |                      | October<br>2016  | <ul> <li>MacBook Pro (13-inch, 2016, Four Thu</li> <li>MacBook Pro (15-inch, 2016)</li> <li>MacBook Pro (13-inch, 2017, Four Thu</li> <li>MacBook Pro (15-inch, 2017)</li> </ul>                                                                                                                                                                                    |

| T2   | APL1027 <sup>[191]</sup> | торичесорет 11.4.4.  |                             |             | ARMv8-<br>A |     |              | TBD | LPDDR4               | December<br>2017 | <ul> <li>iMac Pro 2017</li> <li>MacBook Pro (13-inch, 2018, Four Thu<br/>MacBook Pro (15-inch, 2018)</li> <li>Mac mini (2018)</li> <li>MacBook Air (2018)</li> <li>MacBook Pro (15-inch, 2019)</li> <li>MacBook Pro (13-inch, 2019)</li> <li>MacBook Air (2019)</li> <li>MacBook Pro (16-inch, 2019)</li> <li>Mac Pro (2019)</li> <li>MacBook Air (2020)</li> </ul> |

### **Apple Special Processor**

The Apple M-series coprocessors are

motion coprocessors used by Apple Inc. in their mobile devices. First released in 2013, their function is to collect sensor data from integrated accelerometers, gyroscopes and compasses and offload the collecting and processing of sensor data from the main

Section

Apple Mac

**COMP122**

### Apple Event

November 10, 2020

# Mac

John Ternus VP, Hardware Engineering

### Apple WWDC

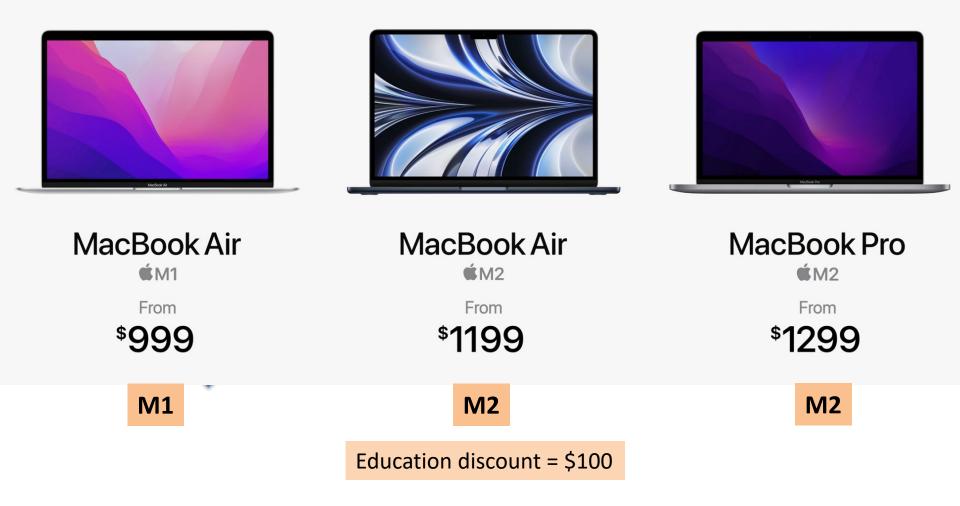

June 6, 2022

#### New MacBooks

### Apple WWDC

STATE UNIVERSITY NORTHRIDGE

**COMP122**

June 6, 2022

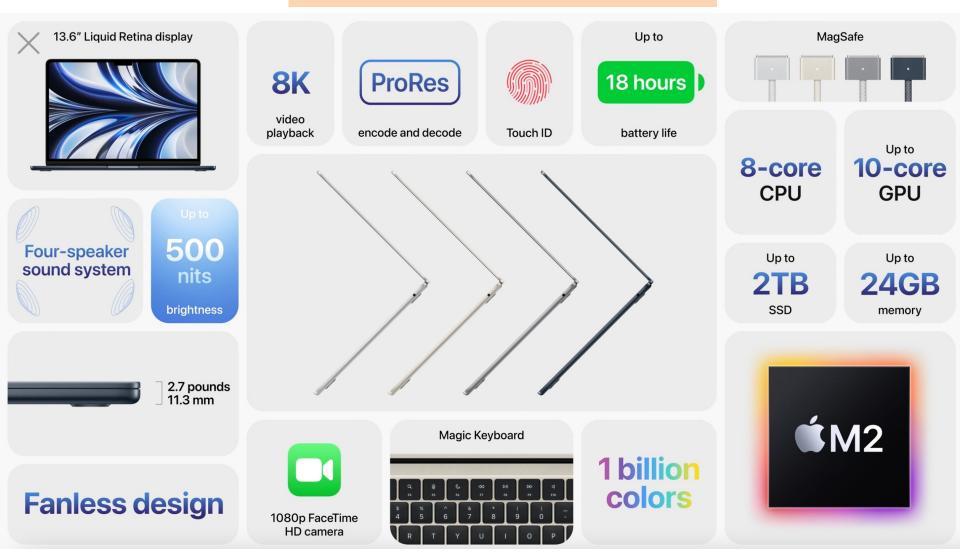

#### New M2 MacBook Air Features

### Apple WWDC

ATE UNIVERSITY NORTHRIDGE

**COMP122**

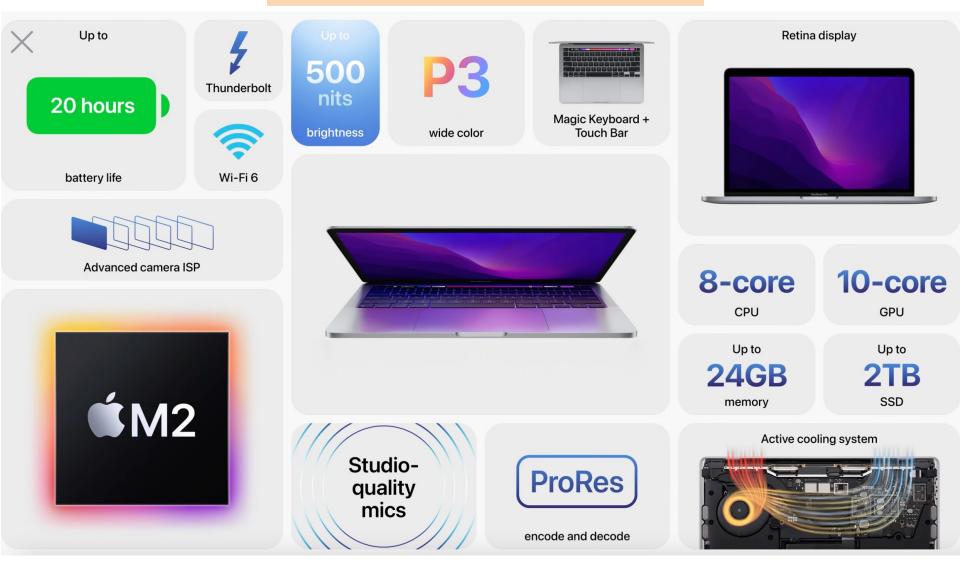

June 6, 2022

#### New M2 MacBook Pro Features

June 6, 2022

#### New M2 MacBook Performance

Apple WWDC

#### **Gaming performance**

MacBook Pro 13" M2

MacBook Pro 13" M1

**39% faster**

MacBook Pro 13" 8th-gen Core i7

3.3x faster

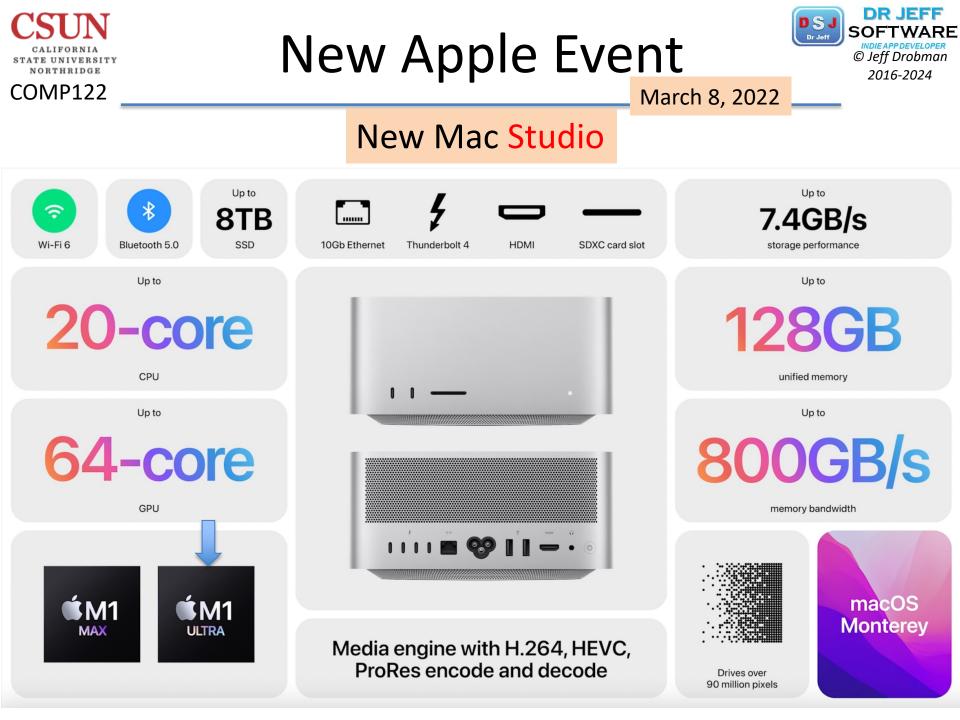

### New Apple Event

March 8, 2022

#### New Mac Lineup

### Mac Studio

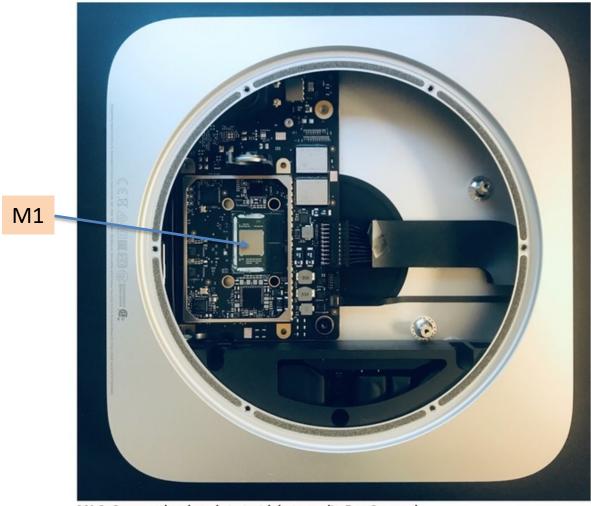

€ M1 Ultra64GB unified memory1TB SSD

Starting at \$3999

### Apple Event

CALIFORNIA STATE UNIVERSITY NORTHRIDGE

### Apple Event

November 10, 2020

CALIFORNIA STATE UNIVERSITY NORTHRIDGE

**COMP122**

### Apple Event

COMP122 November 10, 2020

Laura Metz Mac Product Line Manager

Section

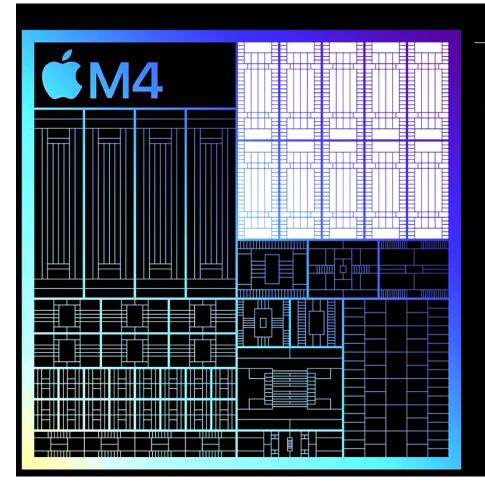

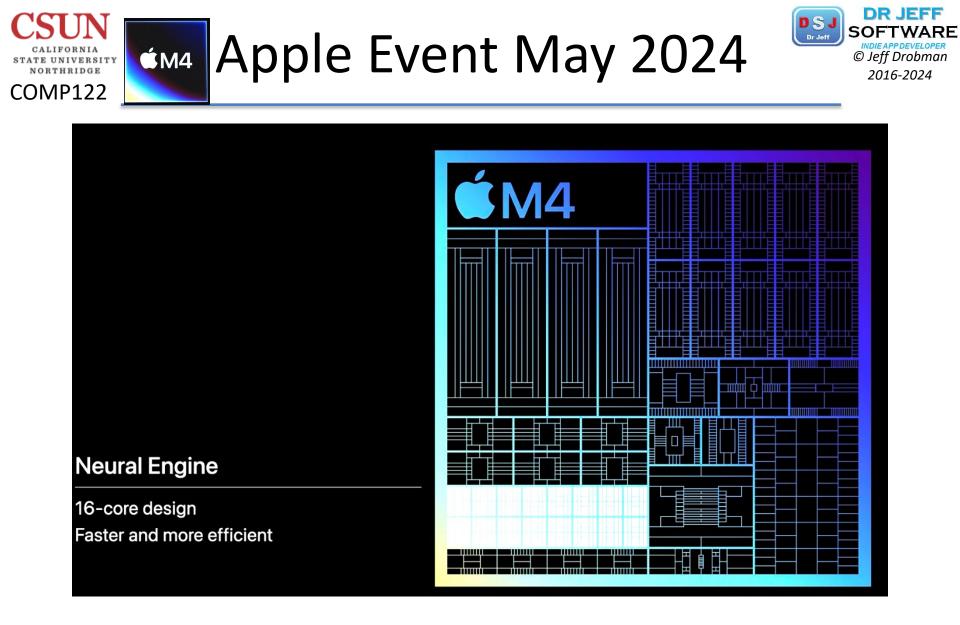

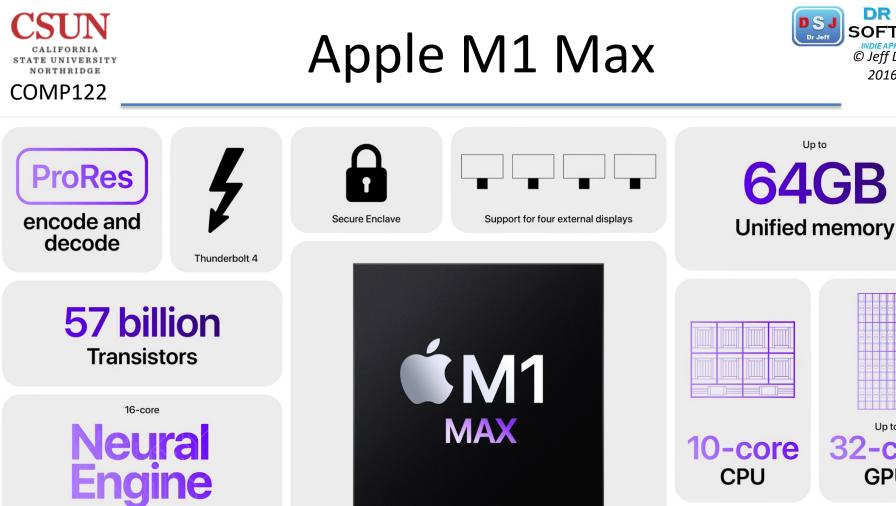

# Apple Chips M4/3/2/1 (ARM v8)

### Apple Event May 2024

faster CPU than M2

### ✓M4 Apple Event May 2024

#### 4 performance cores

Improved branch prediction Wider decode and execution engines Next-generation ML accelerators

#### 6 efficiency cores

Improved branch prediction Deeper execution engine Next-generation ML accelerators

# Apple Event May 2024

#### 10-core GPU

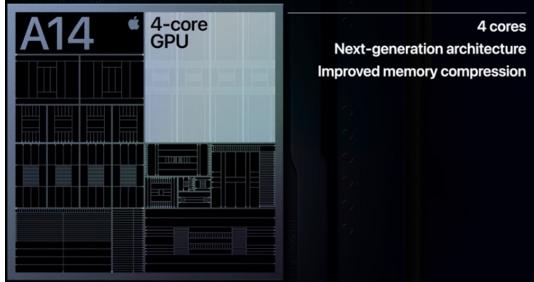

Next-generation architecture Dynamic Caching Mesh shading Ray tracing

ATE UNIVERSITY NORTHRIDGE

**COMP122**

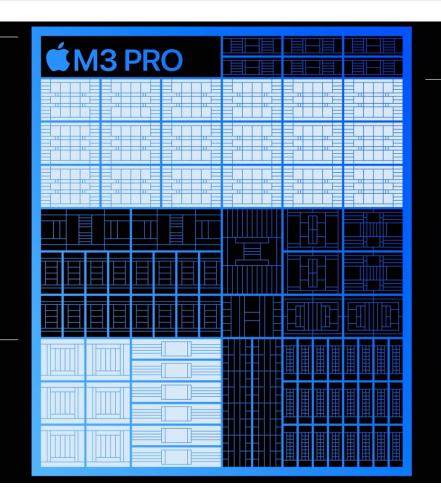

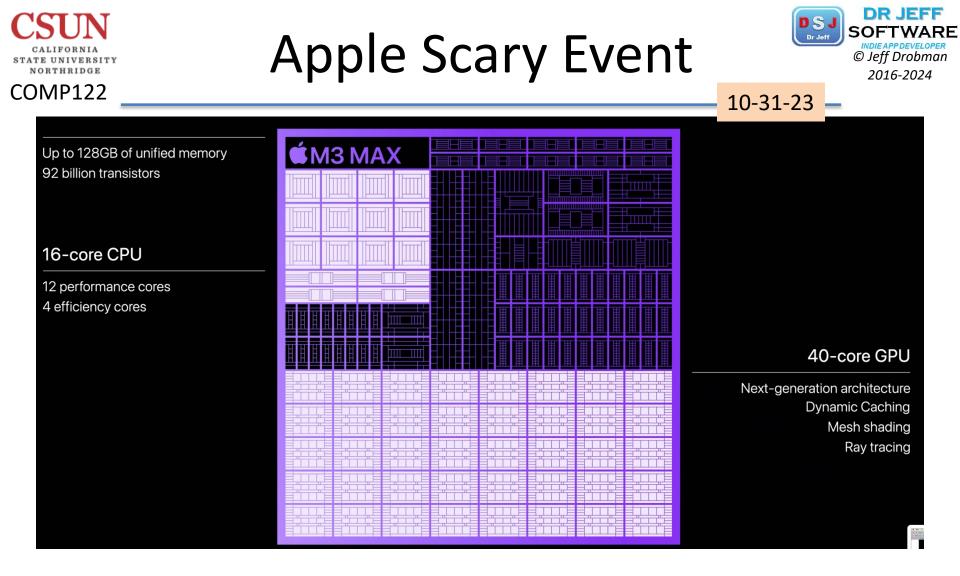

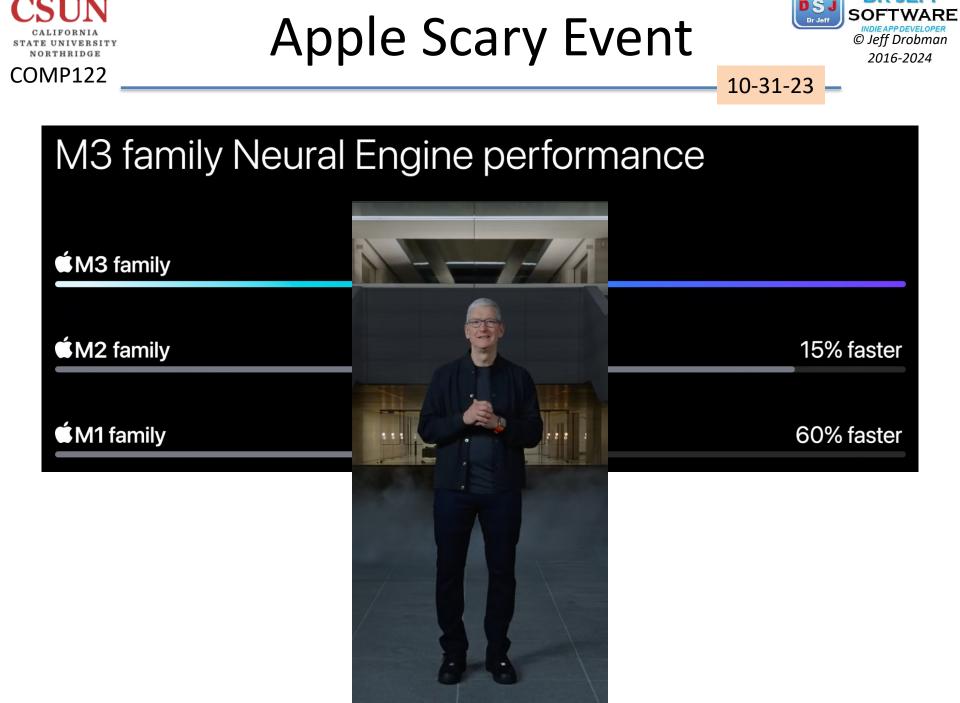

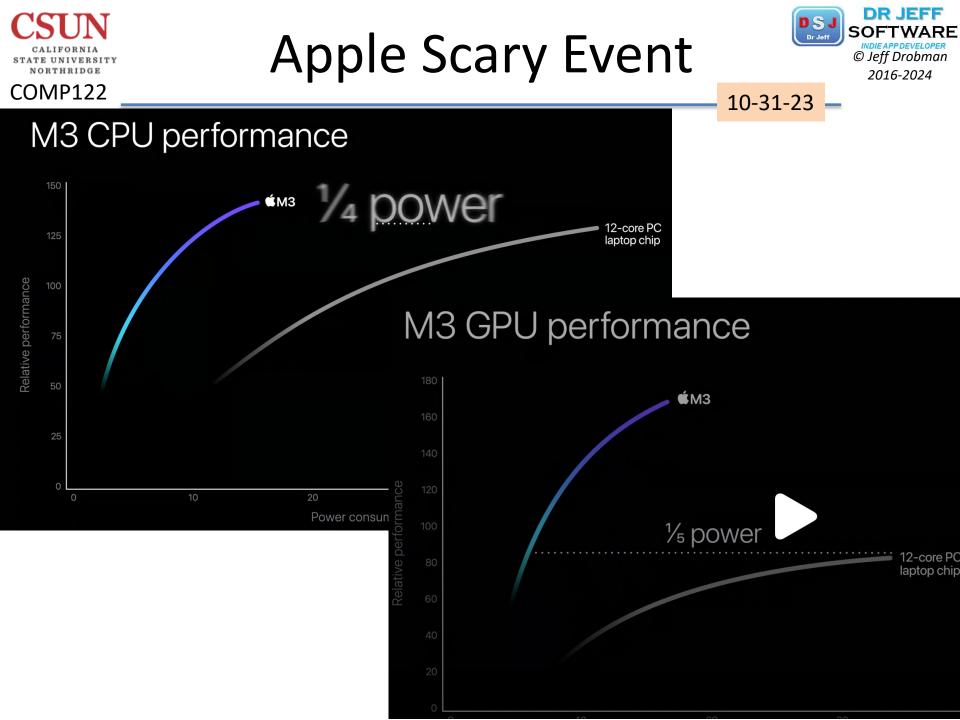

### **Apple Scary Event**

CALIFORNIA STATE UNIVERSITY NORTHRIDGE

**COMP122**

10-31-23

## **Apple Scary Event**

18-core GPU

Dynamic Caching Mesh shading Ray tracing

Next-generation architecture

Up to 40% faster than M1 Pro Up to 10% faster than M2 Pro

10-31-23

Up to 36GB of unified memory 37 billion transistors

CALIFORNIA STATE UNIVERSITY NORTHRIDGE

**COMP122**

#### 12-core CPU

6 performance cores 6 efficiency cores Up to 20% faster than M1 Pro

DR JEFF

June 6, 2022

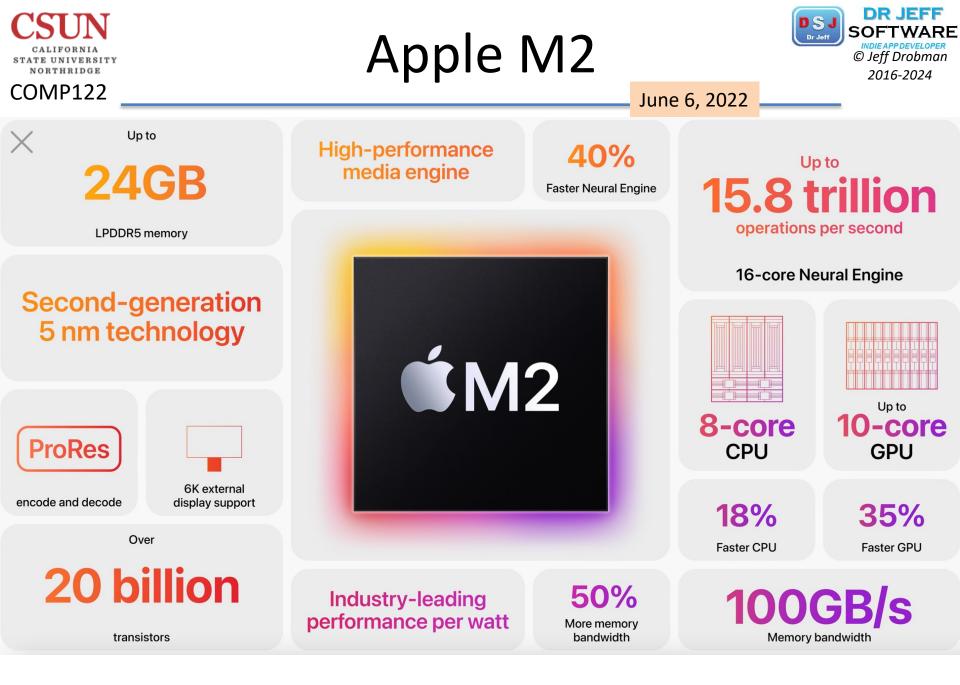

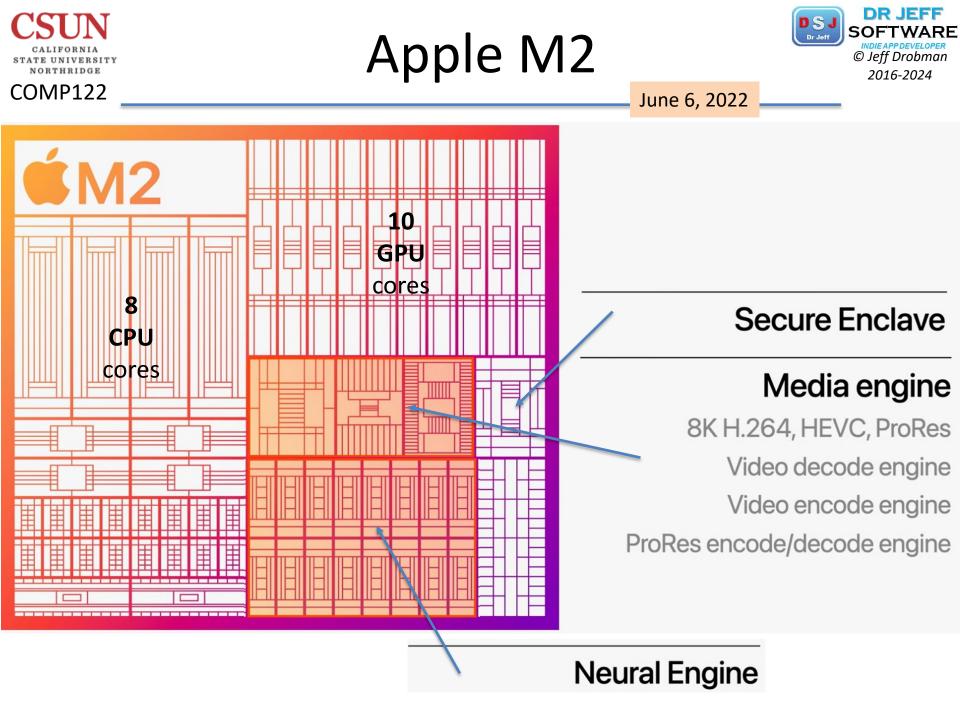

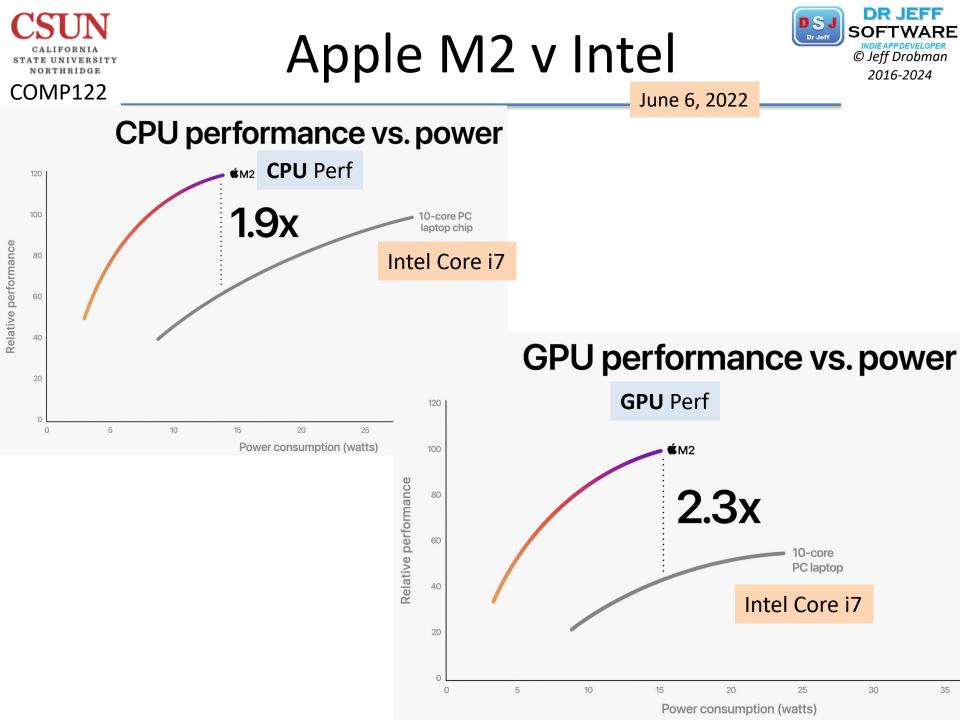

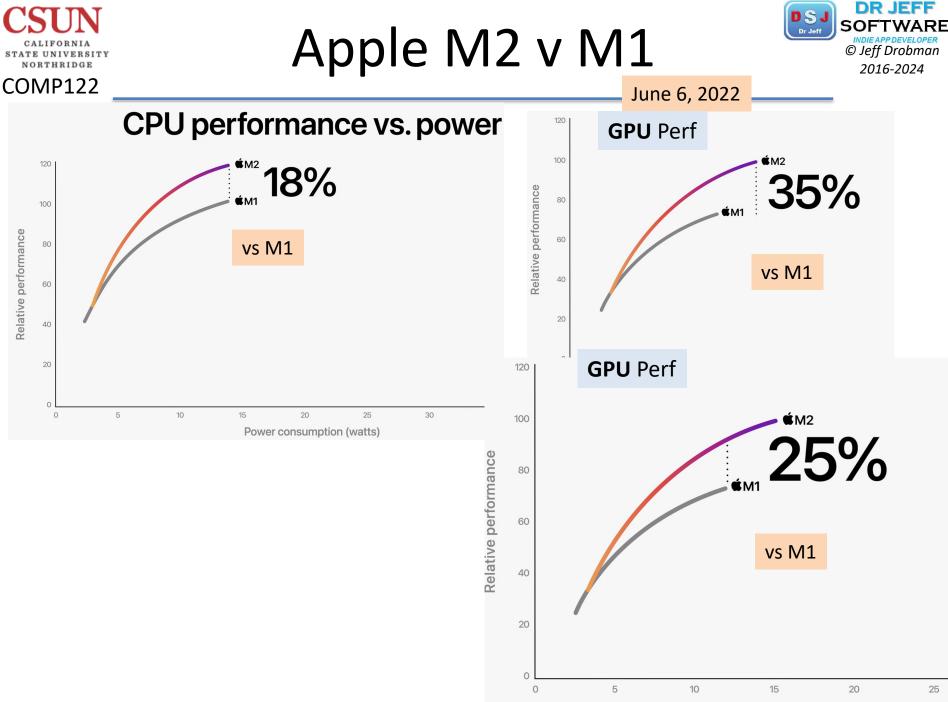

# Apple Chips

#### Second-generation 5 nanometer

June 6, 2022

#### **10 GPU cores**

8-core CPU P

#### 4 high-performance cores

Ultrawide microarchitecture 192KB instruction cache 128KB data cache Shared 16MB cache

NORTHRIDGE

**COMP122**

#### 4 high-efficiency cores

F

Wide microarchitecture 128KB instruction cache 64KB data cache Shared 4MB cache

June 6, 2022

#### 10-core GPU

- Larger L2 cache

- 3.6 teraflops

- 111 gigatexels per second

- 55 gigapixels per second

STATE UNIVERSITY NORTHRIDGE

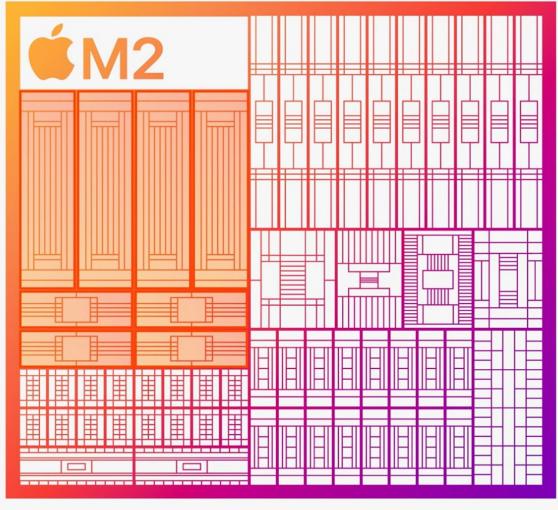

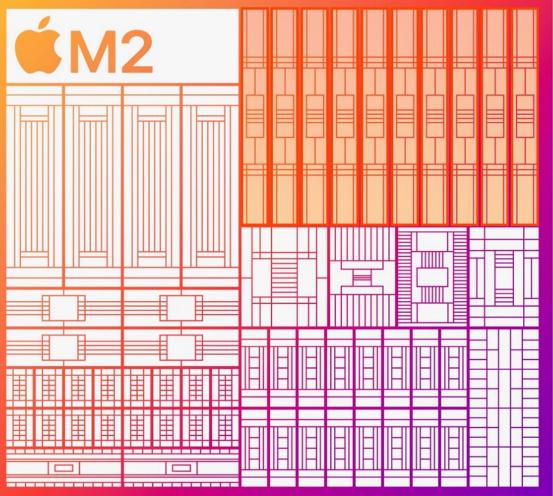

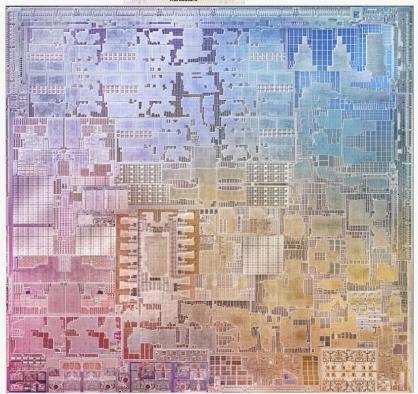

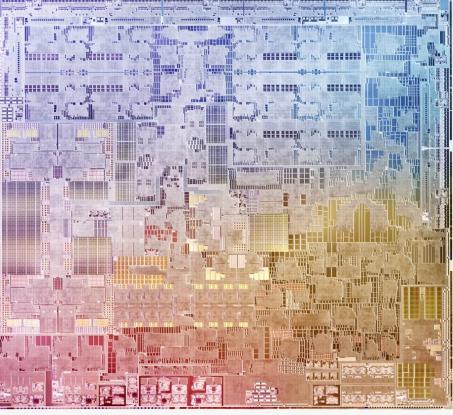

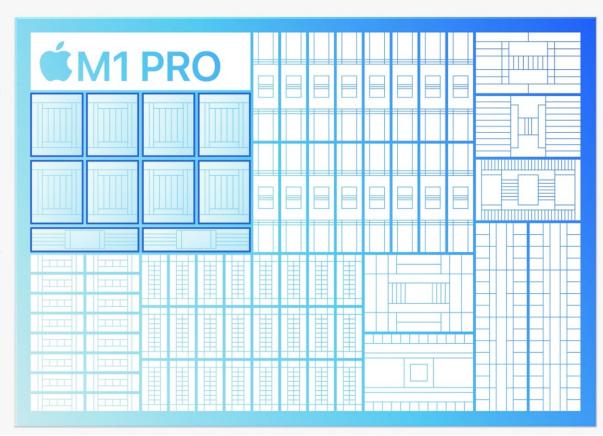

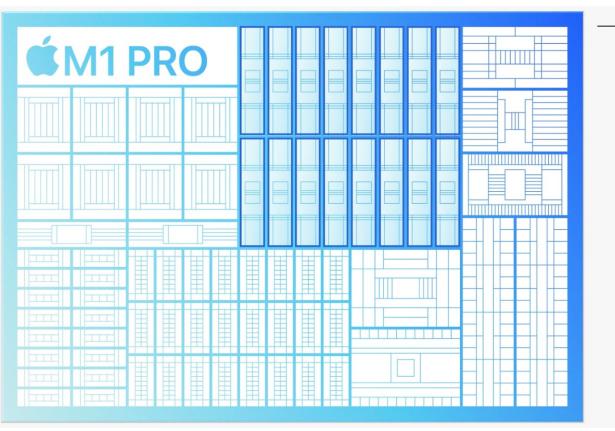

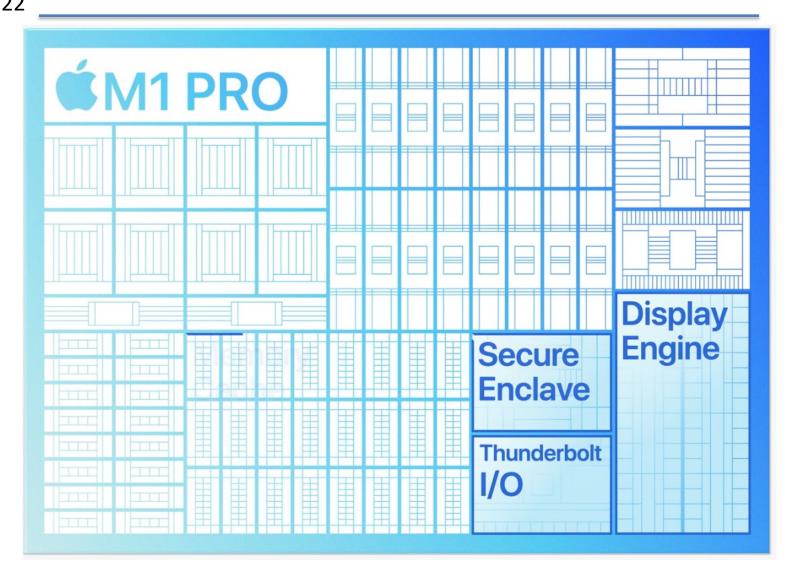

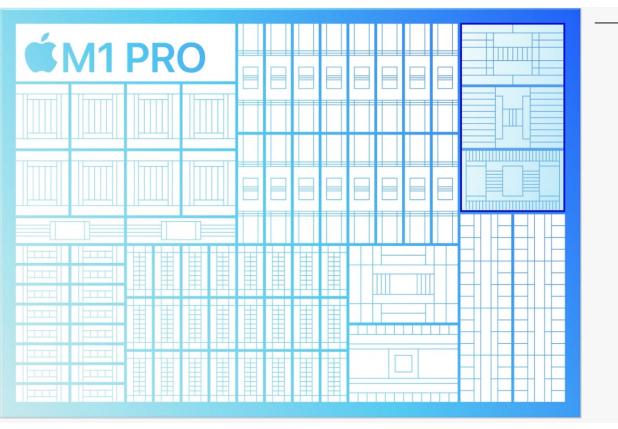

## Apple M2/M1 Die

June 6, 2022

#### Second-generation 5 nanometer

**€**M2

**Transistors**

NORTHRIDGE

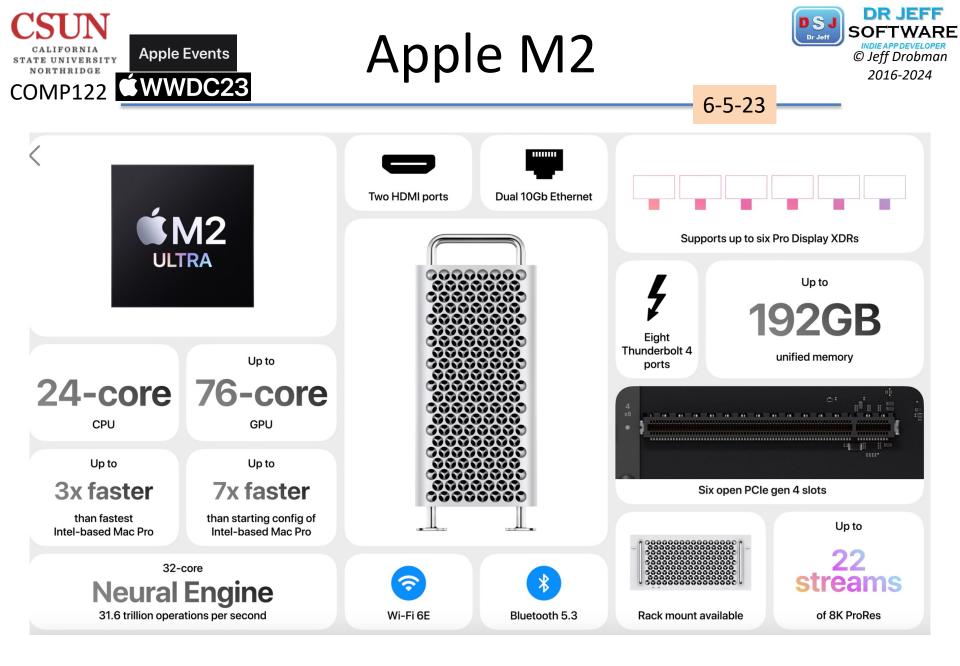

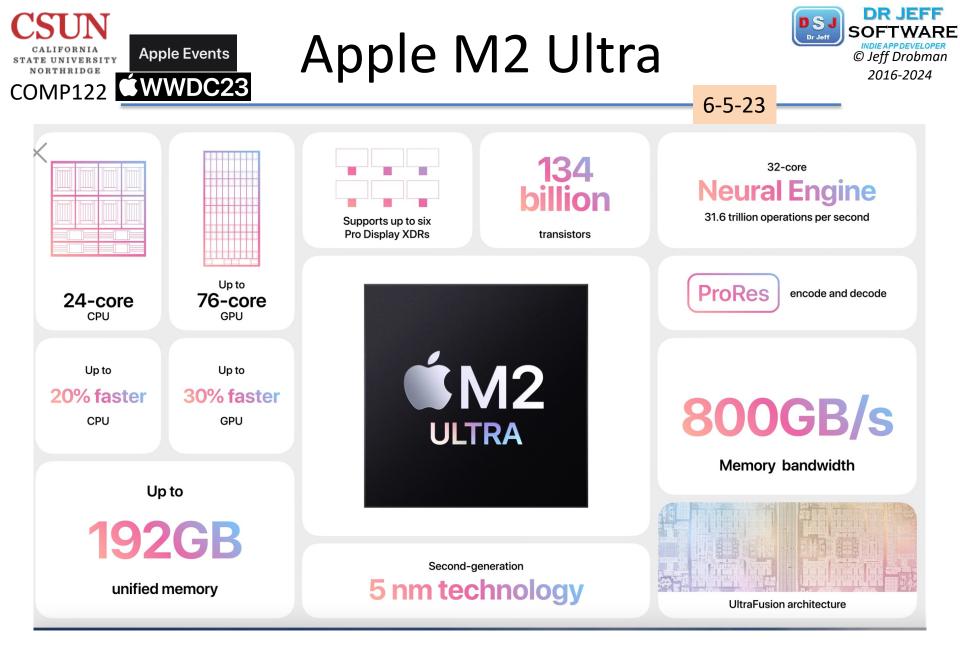

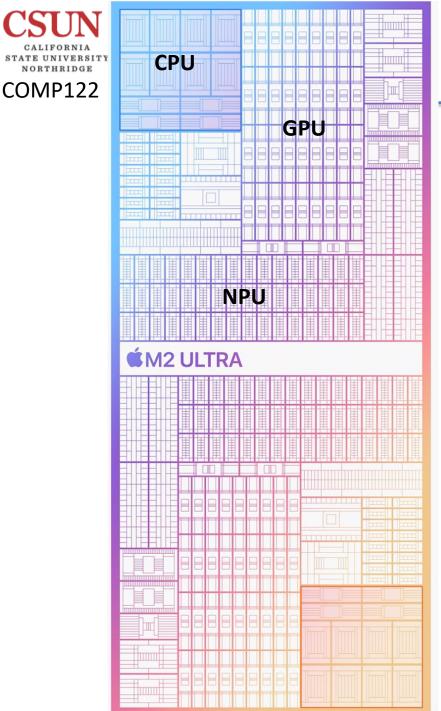

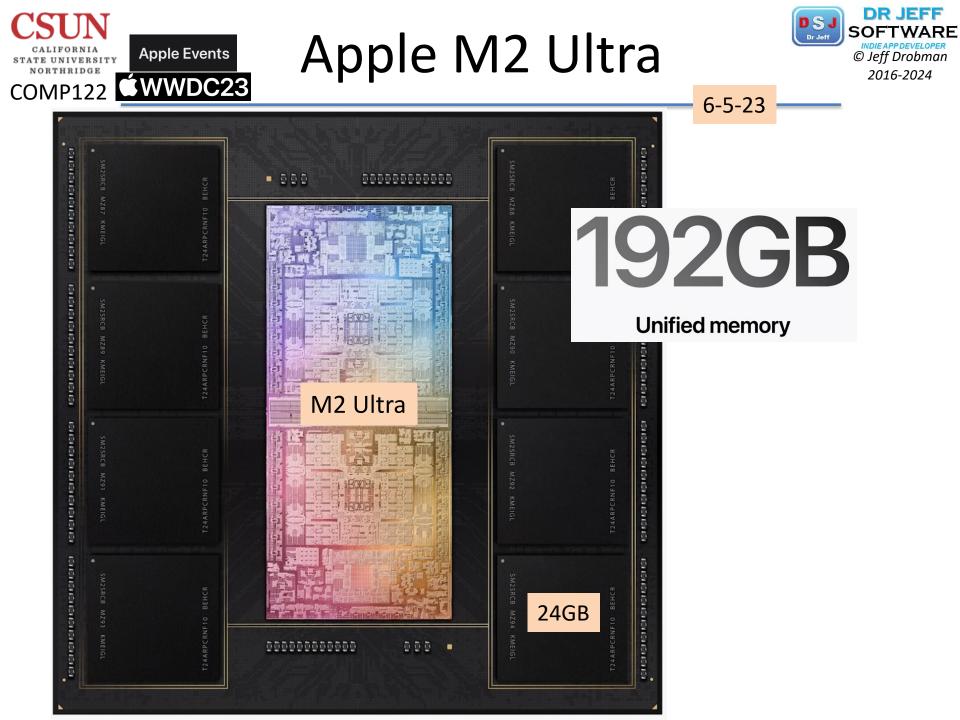

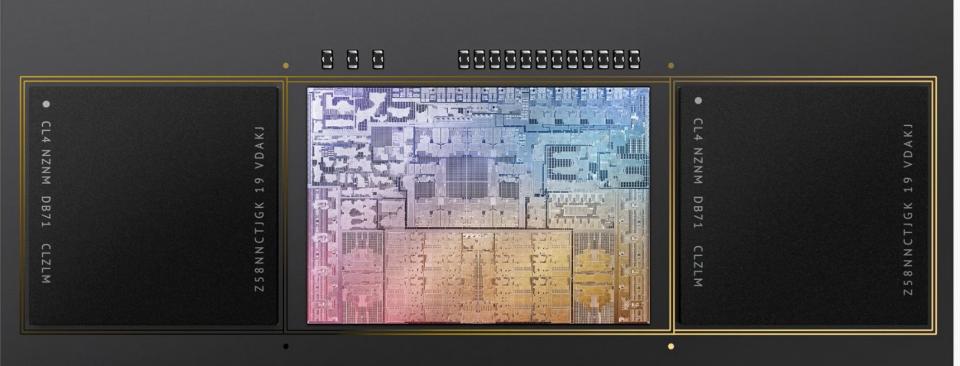

# M2 Ultra

#### Each die (x2)

12 CPU cores (8P+4E)

6-5-23

- 38 CPU cores

- 16 NPU cores

- 67B transistors

#### M2 *Ultra* = 2x M2 *Max*

### Apple M2 Module

June 6, 2022

### 24GB unified memory 121121121 11 121121121 ...... ..... 1 1 1 1 1 1 1211212121212121 1211212121212121

STATE UNIVERSITY NORTHRIDGE

Power consumption (watts)

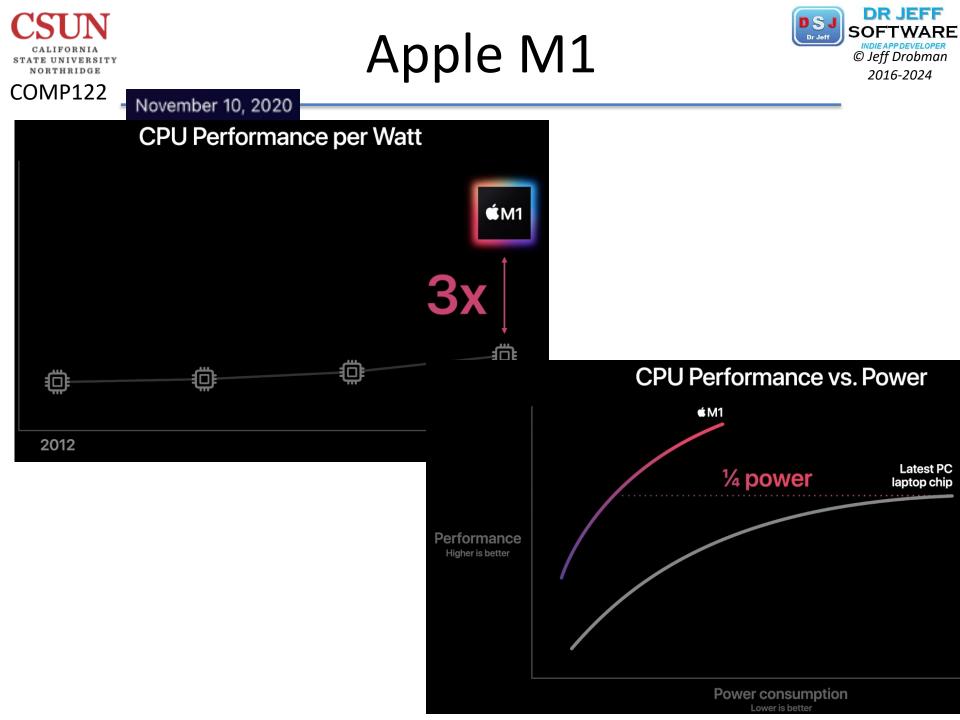

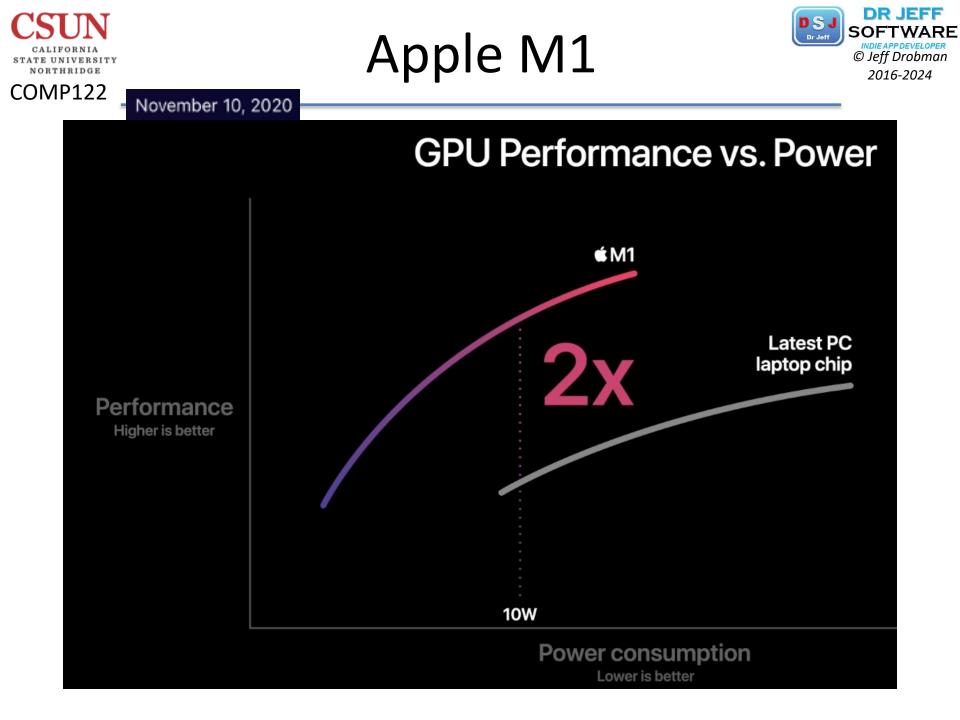

### Industry-leading performance per watt

Advanced image signal processor

Secure Enclave

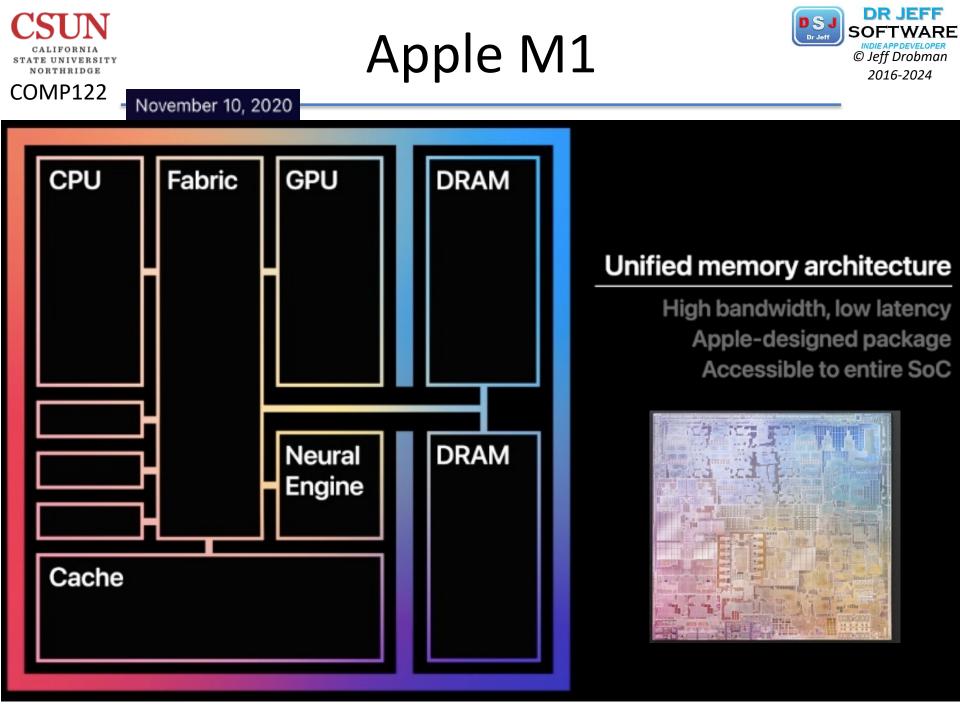

Unified memory architecture

### 5-nanometer process

The first personal computer chip built with this cutting-edge technology.

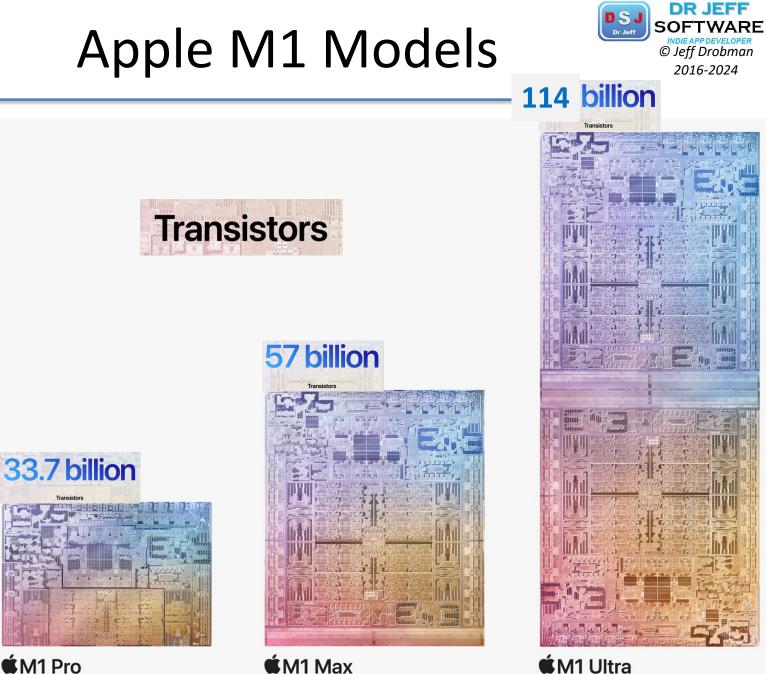

### 16 billion transistors

The most we've ever put into a single chip.

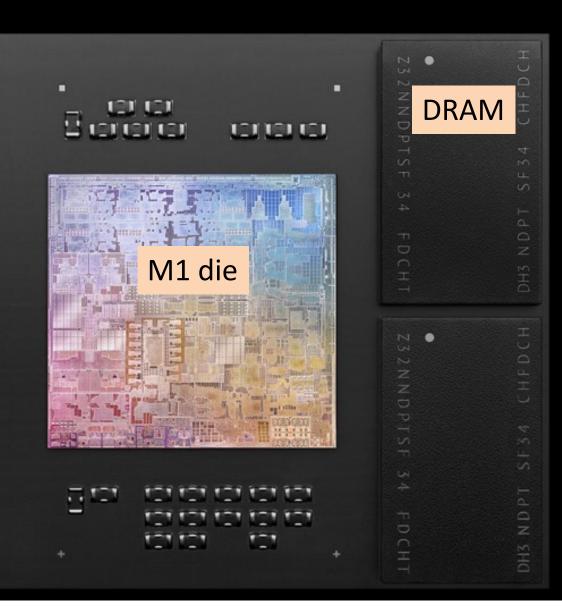

### Apple M1 Module

STATE UNIVERSITY NORTHRIDGE

#### Why is the Intel microchip inferior to the MacBook M1 microchip, in average-user, normal-computing terms?

Jeff Drobman, Lecturer at California State University, Northridge (2016-present) Answered just now

core count. Intel *microchips* come in a broad array of core counts, both CPU and GPU. the Apple M1 has 8 CPU, 8GPU and 16 NPU cores. it would perform comparable to any other such chip — with same number of cores. high-end x86 chips from Intel (Xeon) and AMD (Epyc) will outperform the M1 by a lot, but low end ones will not.

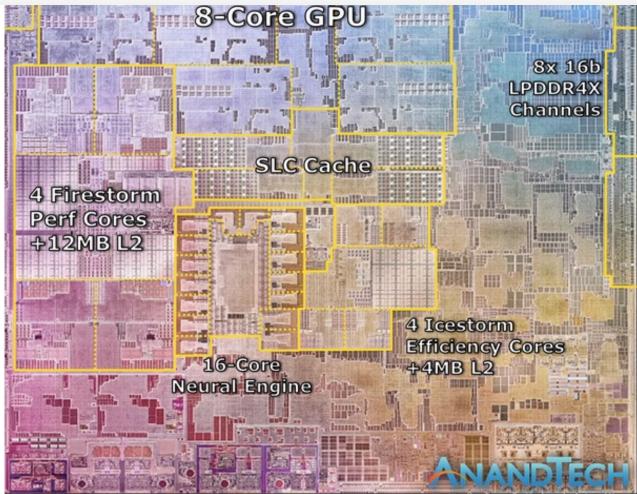

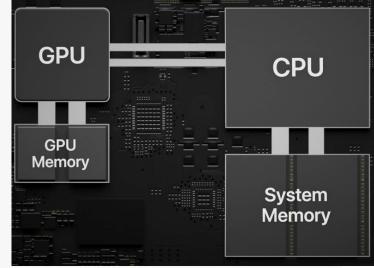

# Apple M1 SoC

#### What's the architectural difference between the low-power and high-performance Apple M1 cores, and can both execute the same instruction sets?

Jeff Drobman, Lecturer at California State University, Northridge (2016-present) Answered just now

the Apple M1 SoC has 8 CPU cores plus 8 GPU, 16 NPU cores. the CPU cores all run the ARMv8 64-bit ISA. while I don't know the specifics, a CPU core can lower its power consumption by lowering its frequency, and maybe by low powering (Sleep) some less often used functions like L2 or L3 cache. A CPU core can only increase its performance via parallelism. SMT with superscalar is the usual way, along with parallel data via SIMD extensions.

٩

RTHRIDGE

**COMP122**

Shresth Sonkar, Mac User since 2014 Answered December 20

- The M1 has a max TDP of 20W and a nominal TDP of 15W. This is way lesser than the previous intel chips used in previous generation — which had 28W nominal TDP. Thus, the heat generation itself is lower

- Since the heat generation is lower, the MacBook Air can handle it via passive cooling using a aluminium heat spreader which carries heat away from processor via conduction instead of convection cooling which uses a fan to blow cool air over the CPU.

- 3. The M1 has asymmetric cores 4 efficiency cores of the octa core design are working on barely 1.3W of power while the rest 4 performance cores are working at 13.8W. This means that the M1 generates less heat in day to day usage to require cooling. Only when the performance cores and GPU are being used, does the power spike up to the 20W figure.

All this makes the M1 a rather highly thermally efficient processor — which doesn't waste energy as heat. It is producing way less heat than intel processors in the same segment of laptops and thus doesn't need a fan.

For comparison, the A14 powering iPhone 12 lineup has 5W TDP, about a third of the Macs. So 5W is not much for a smart phone and 15 is definitely not much for a laptop which has way more surface area for dissipating heat than a smartphone.

SoC's

#### Why don't electronic chip manufacturers have most of the features of a whole computer on one chip similar to the Apple M1 SoC? Is it cost or problems manufacturing it?

Jeff Drobman, Lecturer at California State University, Northridge (2016-present) Answered just now

manufacturers? even Apple does not manufacture chips. if you mean *designers*, like Apple, then many do have multi-core SoC's. Intel is the only *desktop* CPU supplier that also manufactures their own chips. Samsung is the only *mobile* CPU supplier that also manufactures their own chips.

the parts of a "whole computer" that might not fit onto an SoC are large DRAM (best left to separate chips) and I/O devices like sensors. mobile CPU's or SoC's are designed by Qualcomm

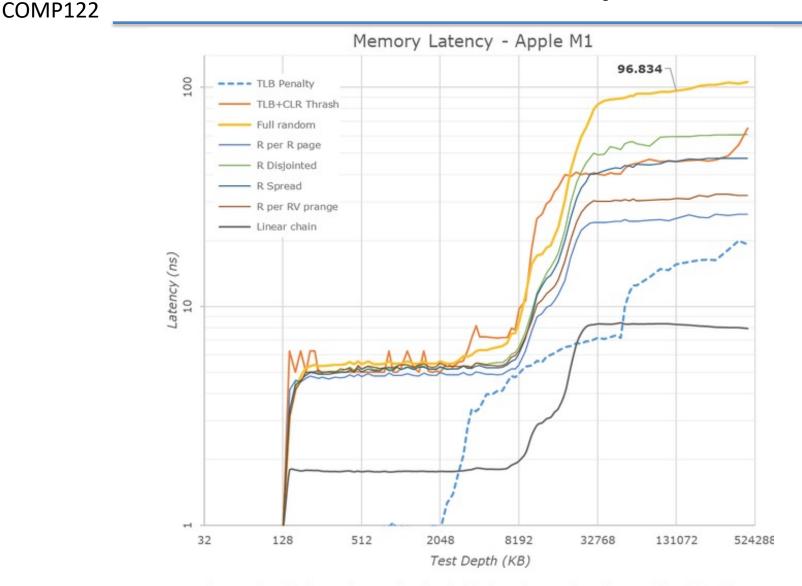

I don't know how big SLC is.

NORTHRIDGE

- It looks physically smaller than the 12MB L2 in the Firestorm cores, but it probably uses noticeably denser SRAM cells. L2 may be optimized for very low latency.

- The memory latency numbers measured by AnandTech show drop-offs at 8MB and 32MB.

- Drop off ar 8MB is probably L2 capacity. However, Firestorm supposedly has 12MB L2, so that suggests some partitioning. I wouldn't be surprised to learn that 4MB is instructiononly to help Rosetta.

- Drop off ar 32MB is likely SLC capacity. 32MB sounds reasonable actually.

Joe Zbiciak replied to your comment on an answer to: "If putting two GPUs in a computer is normal, why isn't putting two CPUs?"

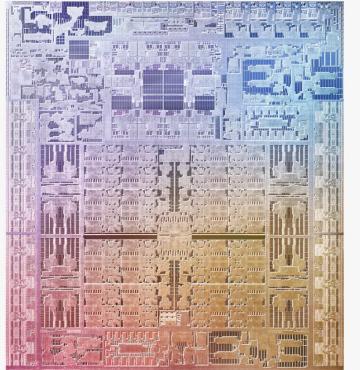

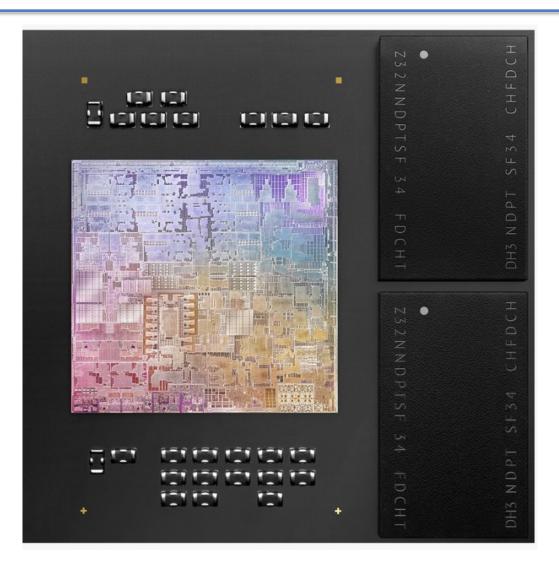

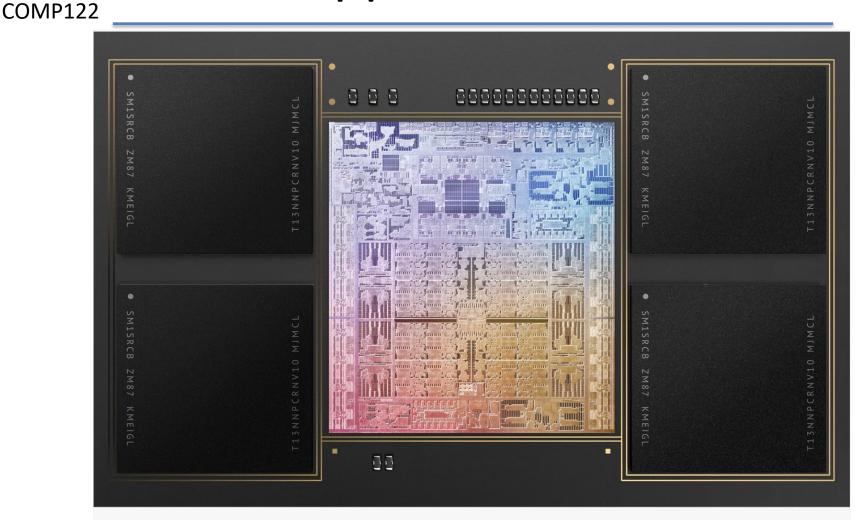

I found an actual picture (rather than illustration) of the M1 with its heat spreader removed. You can see it in the middle-left. It looks a lot like the illustration. Link.

M1 SoC exposed and ready to test (photo credit: Don Scansen)

COMP122

November 10, 2020

CALIFORNIA STATE UNIVERSITY

| Advanced power<br>management       | High-efficiency<br>CPU cores           | High-perfe<br>CPU cores |                         | Secure<br>Enclave | Low-power video<br>playback        | Neural Engine                    |

|------------------------------------|----------------------------------------|-------------------------|-------------------------|-------------------|------------------------------------|----------------------------------|

|                                    | Advanced<br>display engine             |                         |                         |                   | High-performance<br>GPU            |                                  |

| High-bandwidth<br>caches           | display engine                         |                         |                         |                   |                                    | HDR imaging                      |

|                                    | HDR video<br>processor                 |                         |                         |                   |                                    |                                  |

| Cryptography<br>acceleration       |                                        | ń                       | M                       | 1                 |                                    | Gen 4 PCI<br>Express             |

|                                    |                                        |                         |                         |                   | High-performance<br>video editing  |                                  |

| High-performance<br>unified memory | Always-on<br>processor                 |                         |                         |                   | Video curking                      | Performance<br>controller        |

|                                    |                                        |                         |                         |                   | Thunderbolt / USB 4 controller     |                                  |

| Machine learning<br>accelerators   | High-quality image<br>signal processor | Low-power<br>design     | High-perfo<br>NVMe stor |                   | High-efficiency audio<br>processor | Advanced<br>silicon<br>packaging |

COMP122

CALIFORNIA STATE UNIVERSITY NORTHRIDGE

#### November 10, 2020

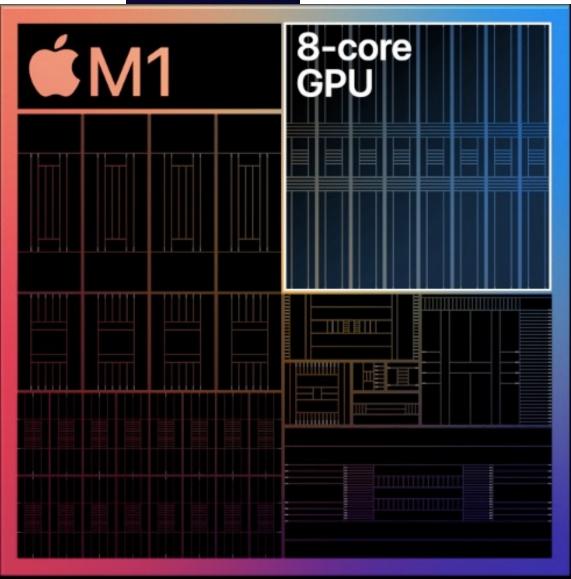

#### Up to 8 cores

128 execution units Up to 24,576 concurrent threads 2.6 teraflops 82 gigatexels/second 41 gigapixels/second

### M1 Memory

NORTHRIDGE

There's a lot of unknown in AnandTech's die labeling. Also, we don't know Apple's SLC policy or interconnect architecture. Apple has demonstrated repeatedly that they're more than happy to ignore ARM's standard mechanism and methodologies.

### M1 Benchmark

|              | Apple iPad pro<br>12.9 (M1) |       | Microsoft Surface Pro 7<br>(Intel Core i5-1035G4 10th<br>Gen) |

|--------------|-----------------------------|-------|---------------------------------------------------------------|

| Single-Core  | 1714                        | 1740  | 862                                                           |

| Multi-Core   | 7272                        | 7694  | 3104                                                          |

| OpenCL Score | 20887                       | 18347 | 7801                                                          |

Apple's M1-based iPad Pro's benchmarks are in line with other M1-based systems.

NORTHRIDGE

**COMP122**

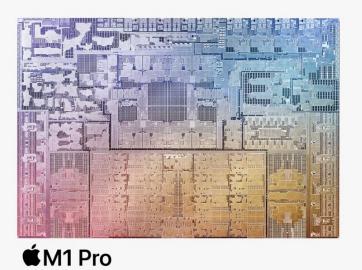

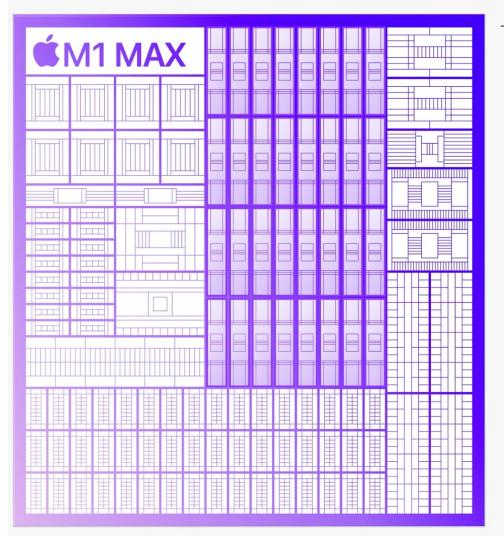

#### 8 high-performance cores

STATE UNIVERSITY NORTHRIDGE

**COMP122**

Ultra-wide execution architecture 192KB instruction cache 128KB data cache 24MB L2 cache

#### 2 high-efficiency cores

Wide execution architecture 128KB instruction cache 64KB data cache 4MB L2 cache

Faster CPU performance than M1

CALIFORNIA STATE UNIVERSITY NORTHRIDGE

**COMP122**

#### 16-core GPU

2048 execution units Up to 49,512 concurrent threads 5.2 teraflops 164 gigatexels/second 82 gigapixels/second

STATE UNIVERSITY NORTHRIDGE

**COMP122**

#### Media Engine

Hardware-accelerated H.264, HEVC, ProRes, and ProRes RAW

Video decode engine

Video encode engine

ProRes encode/decode engine

Multiple streams of

4K and 8K ProRes video

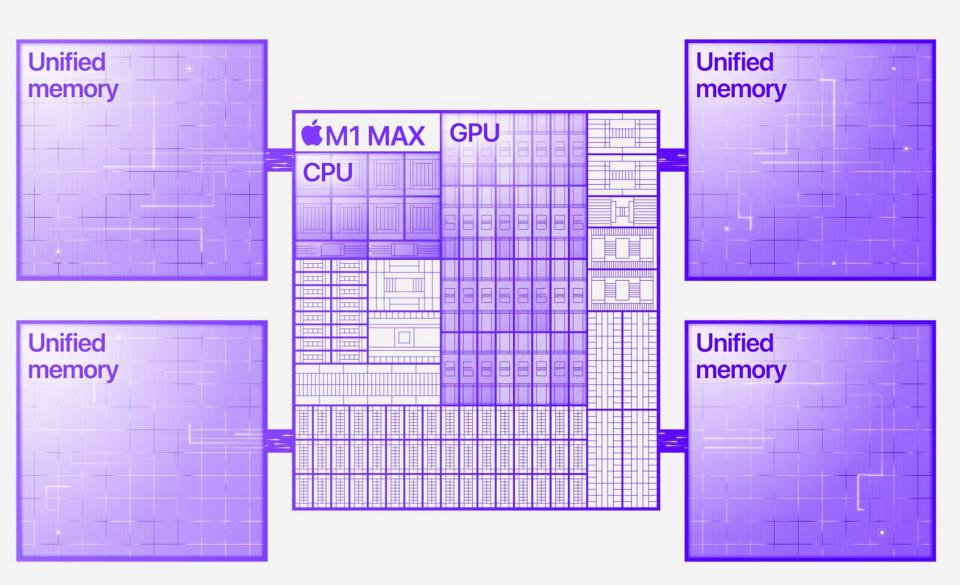

### Apple M1

#### 32GB unified memory

ATE UNIVERSITY NORTHRIDGE

**COMP122**

High bandwidth, low latency 256-bit LPDDR5 interface Apple-designed custom package

CALIFORNIA STATE UNIVERSITY NORTHRIDGE

**COMP122**

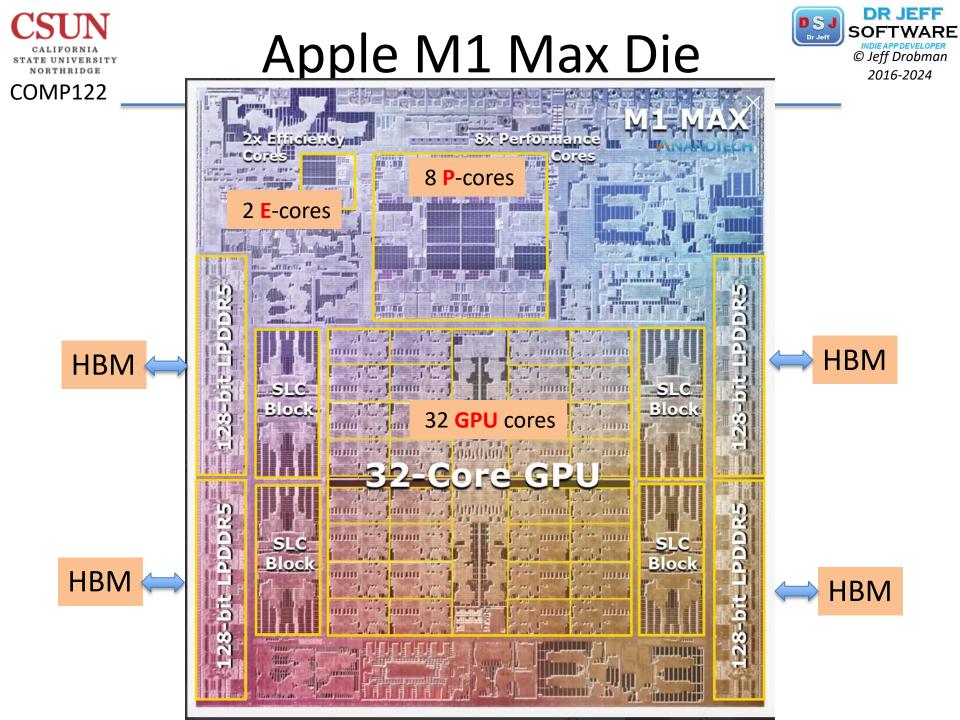

32-core GPU

4096 execution units Up to 98,304 concurrent threads 10.4 teraflops 327 gigatexels/second 164 gigapixels/second

#### 64GB unified memory

STATE UNIVERSITY NORTHRIDGE

> High bandwidth, low latency 512-bit LPDDR5 interface Apple-designed custom package

11 trillion operations per second

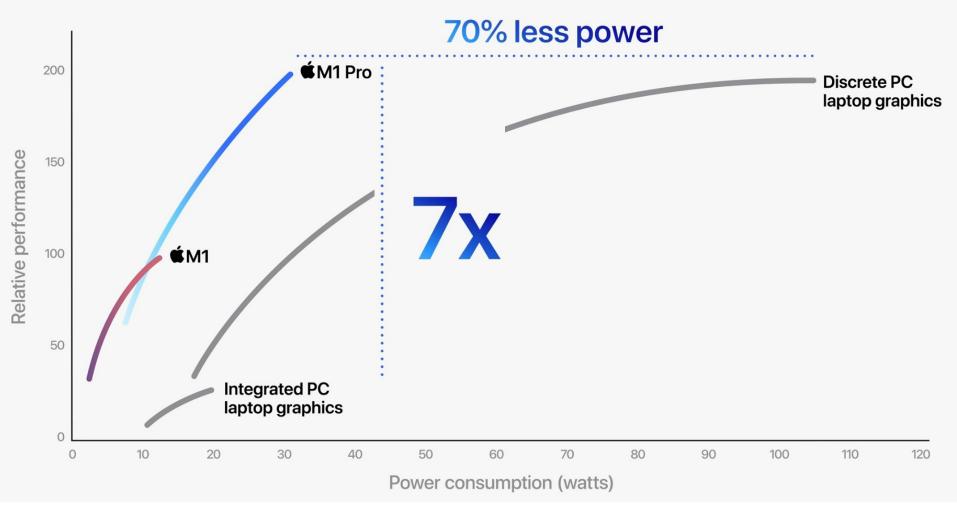

Industry-leading performance per watt **5 nm process**

#### 400GB/s Memory bandwidth

Up to

32-core

GPU

Up to

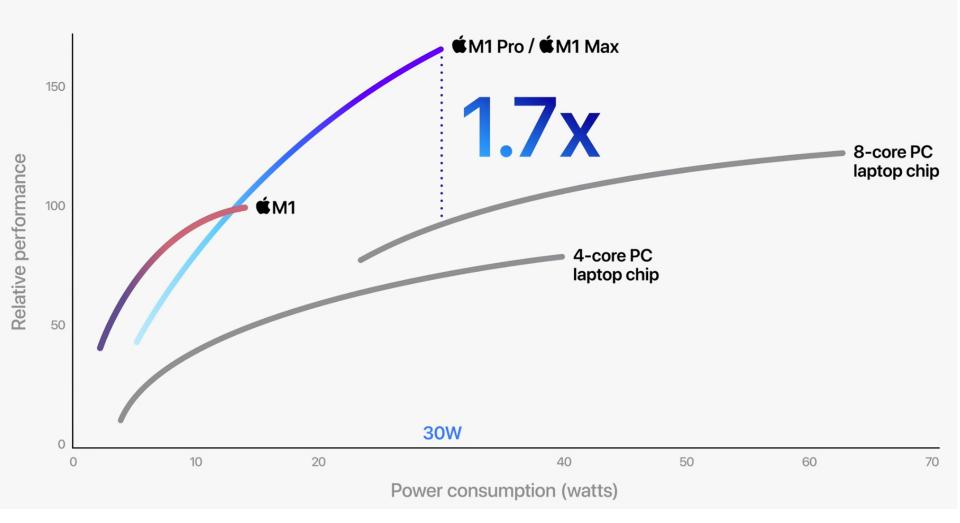

#### CPU performance vs. power

## Hardware-verified secure boot Runtime anti-exploitation Fast in-line encryption

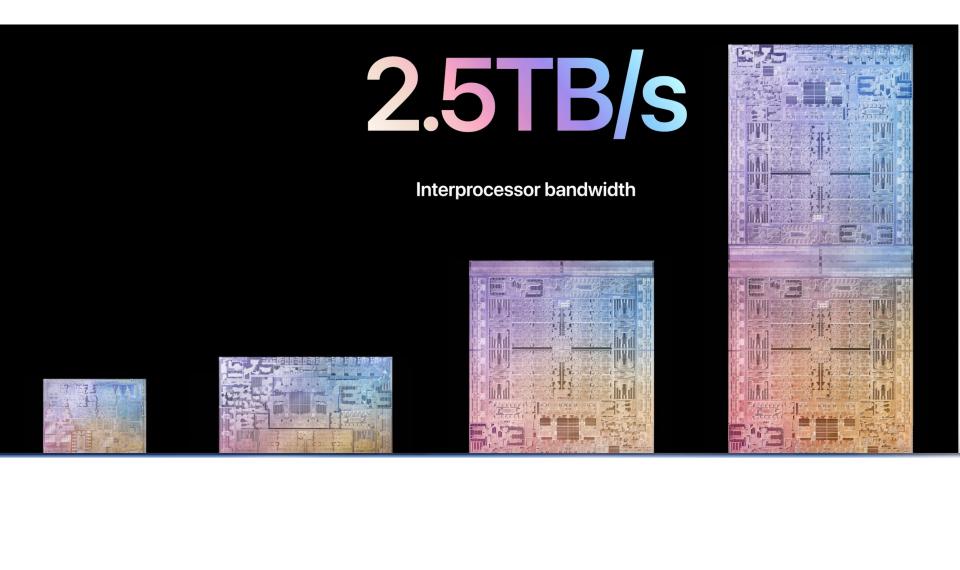

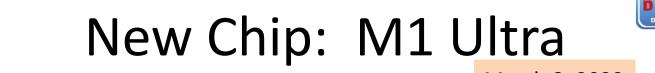

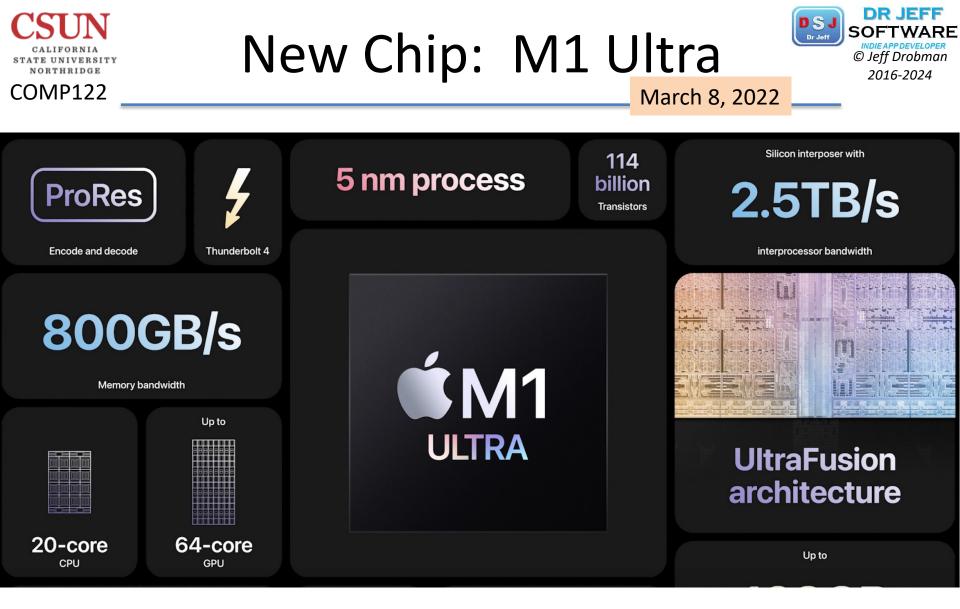

New Chip: M1 Ultra

STATE UNIVERSITY NORTHRIDGE

**COMP122**

**Ś**М1

ALIFORNIA STATE UNIVERSITY NORTHRIDGE

**COMP122**

**M**1 Pro

**É**M1 Ultra

ATE UNIVERSITY NORTHRIDGE

New Chip: M1 Ultra

#### 20-core CPU

#### 16 high-performance cores

Ultrawide execution architecture 192KB instruction cache 128KB data cache 48MB total L2 cache

#### 4 high-efficiency cores

Wide execution architecture 128KB instruction cache 64KB data cache 8MB total L2 cache

|             | 1            | _  | <b></b>      |            |                 |   |    |   |   |    |   |   |   |    |   |   |

|-------------|--------------|----|--------------|------------|-----------------|---|----|---|---|----|---|---|---|----|---|---|

|             | $\mathbb{H}$ | Π  | $\mathbb{H}$ | Ш          |                 |   |    |   |   |    |   |   |   |    |   |   |

|             | Щ            | Щ  | Ш            | Щ          |                 | Ξ | Η  | Η | Н | Н  | Н |   |   | 11 |   |   |

|             |              |    |              |            |                 |   |    |   |   |    |   |   |   | 11 |   |   |

|             |              |    |              |            |                 |   |    |   |   |    |   |   |   | h  |   |   |

|             | J            |    | P            |            |                 |   |    |   |   |    | Ξ | Ξ |   | J  |   |   |

|             |              |    |              |            |                 |   |    |   |   |    |   |   |   |    |   | T |

|             |              |    |              |            |                 |   |    |   |   |    |   |   |   |    |   |   |

|             |              |    |              |            |                 |   |    |   |   |    | Ξ |   |   | I  | 1 |   |

|             |              |    |              | i T T      |                 |   |    |   |   |    |   |   |   |    | T |   |

|             |              |    |              |            |                 |   |    |   |   |    |   |   |   |    |   |   |

|             |              |    |              |            |                 |   |    |   |   |    |   |   |   |    |   |   |

|             |              |    |              |            |                 |   |    |   |   |    |   |   | E |    |   |   |

|             |              |    |              |            |                 |   |    |   |   |    |   |   |   |    |   |   |

|             |              |    |              |            |                 |   |    |   |   |    |   |   |   |    |   |   |

|             |              |    |              |            |                 |   |    |   |   |    |   |   |   |    |   |   |

|             |              |    |              |            | #               |   |    |   | Ħ |    | Ħ |   |   |    |   |   |

|             |              |    |              |            |                 |   |    |   |   |    |   |   |   |    |   |   |

|             | 1 HE         | 12 | 172          | 144        | H.              | ÷ | 1H | - | H | HE | Ħ |   |   |    |   |   |

|             |              |    |              |            |                 |   |    |   |   |    |   |   |   |    |   |   |

| <b>G</b> M1 | U            | Ľ  | Γŀ           | R/         | ٩.              |   |    |   |   |    |   |   |   |    |   |   |

| <b>É</b> M1 | U            | L  |              | <b>₹</b> / | <b>∖</b><br>  _ |   |    |   |   |    |   |   |   |    |   |   |

| <b>G</b> M1 | U            |    |              | <b>₹</b> / | •               |   |    |   |   |    |   |   |   |    |   |   |

| <b>©</b> M1 | U            |    |              | ₹ <i>/</i> | •               |   |    |   |   |    |   |   |   |    |   |   |

|             |              |    |              | ₹ <i>/</i> |                 |   |    |   |   |    |   |   |   |    |   |   |

|             |              |    |              | 2/4        |                 |   |    |   |   |    |   |   |   |    |   |   |

|             |              |    |              |            |                 |   |    |   |   |    |   |   |   |    |   |   |

|             |              |    |              |            |                 |   |    |   |   |    |   |   |   |    |   |   |

|             |              |    |              |            |                 |   |    |   |   |    |   |   |   |    |   |   |

|             |              |    |              |            |                 |   |    |   |   |    |   |   |   |    |   |   |

|             |              |    |              |            |                 |   |    |   |   |    |   |   |   |    |   |   |

|             |              |    |              |            |                 |   |    |   |   |    |   |   |   |    |   |   |

|             |              |    |              |            |                 |   |    |   |   |    |   |   |   |    |   |   |

|             |              |    |              |            |                 |   |    |   |   |    |   |   |   |    |   |   |

March 8, 2022

New Chip: M1 Ultra

#### 64-core GPU

8192 execution unitsUp to 196,608 concurrent threads21 teraflops660 gigatexels/second330 gigapixels/second

| Π         |    | ΠI           |    | Π |     |   |      |   |   |   |   |   | 1        |  |

|-----------|----|--------------|----|---|-----|---|------|---|---|---|---|---|----------|--|

| Щ         | ļ. | Щ            |    |   |     |   |      |   |   | E | B |   |          |  |

| $\square$ | Ι  | $\mathbb{I}$ | ]] |   |     |   |      |   |   |   |   |   | #"<br>]} |  |

|           |    |              |    |   |     |   |      |   |   |   |   | F |          |  |

|           |    |              |    |   |     |   | 8    |   |   |   |   |   |          |  |

|           |    |              |    |   |     |   |      | Π | Π |   | 8 |   |          |  |

|           |    |              |    |   |     |   |      | B |   |   |   |   |          |  |

|           |    |              |    |   |     | Π |      |   |   |   |   |   |          |  |

|           |    |              |    |   |     |   |      |   |   |   |   |   |          |  |

|           |    |              |    |   |     |   | 1111 |   |   |   |   | E |          |  |

|           |    |              |    |   |     |   |      |   |   |   |   |   |          |  |

|           |    |              |    |   |     |   |      |   |   |   |   |   |          |  |

| 3         | M  | 1            | U  |   | R/  |   |      |   |   |   |   |   |          |  |

|           | M  | 1            | U  |   | 2/4 |   |      |   |   |   |   |   |          |  |

|           | M  |              | U  |   | R/A |   |      |   |   |   |   |   |          |  |

|           | M  |              |    |   | 2/  |   |      |   |   |   |   |   |          |  |

|           | M  |              |    |   | 2/  |   |      |   |   |   |   |   |          |  |

|           |    |              |    |   |     |   |      |   |   |   |   |   |          |  |

|           |    |              |    |   |     |   |      |   |   |   |   |   |          |  |

|           |    |              |    |   |     |   |      |   |   |   |   |   |          |  |

March 8, 2022

Mac Studio M1 Ultra

90% Faster

Mac Pro 16-core Xeon

Mac Studio M1 Ultra

80% Faster

Mac Pro Radeon Pro W6900X

Section

## Apple Chip Fab/Mfg

#### TSMC 4nm

#### Apple Orders 4nm Chip Production for Next-Generation Macs

Tuesday March 30, 2021 12:35 am PDT by Sami Fathi

Apple has booked the initial production capacity of 4nm chips with long-time supplier TSMC for its next-generation Apple silicon, according to industry sources cited in a new report today from *DigiTimes*.

## Apple & TSMC

Apple has already booked the initial capacity of TSMC's N4 for its new-generation Mac series, the sources indicated. Apple has also contracted TSMC to make its nextgeneration <u>iPhone</u> processor dubbed A15, built using the foundry's N5 Plus or N5P process node, the sources said.

TSMC is expected to kick off production for Apple's A15 chip that will power the upcoming <u>iPhone 13</u> series by the end of May, the sources noted.

The latest Apple silicon, the <u>M1</u> chip, is the first of its kind in the industry based on the 5nm process. The A14 Bionic chip in the <u>iPad Air</u> and <u>iPhone 12</u> lineup is also based on the 5nm process. According to the report, Apple is already looking to the 4nm chip process for its next-generation Apple silicon.

A timeframe for when these new 4nm chips will debut isn't provided, but *DigiTimes* does report that TSMC will move to volume production of the new process in Q4 of 2021, ahead of the previously set 2022 timeframe. Additionally, Apple plans to use an enhanced version of the 5nm process for the A15 chip in the iPhone 13, with production set to get underway by the end of May.

The smaller process reduces the chips' actual footprint and provides better efficiency and performance. Apple's expected to launch <u>multiple new Macs</u> this year with more powerful Apple silicon chips; however, there's no indication that any will be based on the 4nm process.

## TSMC \$ Apple

#### COMP122 Taiwan Semiconductor asked for 2023 price increase from Apple, tech giant said no: report

Sep 28, 2022 11:23 AM ET | **Taiwan Semiconductor Manufacturing Company Limited (TSM)** | Chris Ciaccia, SA News Editor

Taiwan Semiconductor (NYSE:TSM) is slated to raise prices on its customers starting in 2023, but the company's largest customer, Apple (NASDAQ:AAPL), has reportedly told the global foundry no deal.

According to Chinese news outlet Economic Daily News, Taiwan Semiconductor (TSM) wanted to increase the price of the process for its 3 nm process by 3%, which may be used in the A17 chip in some of Apple's (AAPL) Mac computers and perhaps next year's iPhone. However, the tech giant refused and said no, the news outlet said, citing sources. In May, it was reported that Taiwan Semiconductor Manufacturing (TSM) had started to tell some of its customers that it will raise its prices between 5% and 9%, starting next year, due to inflation concerns, rising costs and its expansion.

Cupertino, California-based Apple (AAPL) is Taiwan Semiconductor's (TSM) largest customer and some reports have suggested that it accounts for as much as 25% of the global foundry's annual revenue.

#### 25%

COMP122

### TSMC 3nm

SemiWiki.com The Open Forum for Semiconductor Professionals 8-17-22

TSMC's Initial 3nm HVM Yield To Be Better Than Its 5nm

TSMC **N3e** is the HPC version for Intel, AMD, Nvidia, etc... The SoC companies Apple, Mediatek, will use **N3**. Please remember that TSMC sets expectations on the conservative so they don't disappoint. According to my sources N3 for Apple was frozen in December and the N3e process is now frozen with HVM starting in 1H 2023.

> Apple now in production (HVM) with 4nm

Apple MacOS

COMP122

#### New Mac OS

November 10, 2020

#### New Mac OS

November 10, 2020

#### Hardware-verified secure boot Automatic high-performance encryption macOS run-time protections

Software

### Apple Software iOS 6-7-21

### WWDC 21

# iOS 15