# **COMP 122**

Rev 2-22-22

# ASSEMBLY Programming/ISA ARM

### Dr Jeff Drobman

website drjeffsoftware.com/classroom.html

email <u>jeffrey.drobman@csun.edu</u>

## ARM Index

- **♦** ARM History → slide 3

- **♦** ARM CPU Models → slide 12

- **♦** ARM OS's → slide 54

- ❖ISA  $\rightarrow$  slide 58

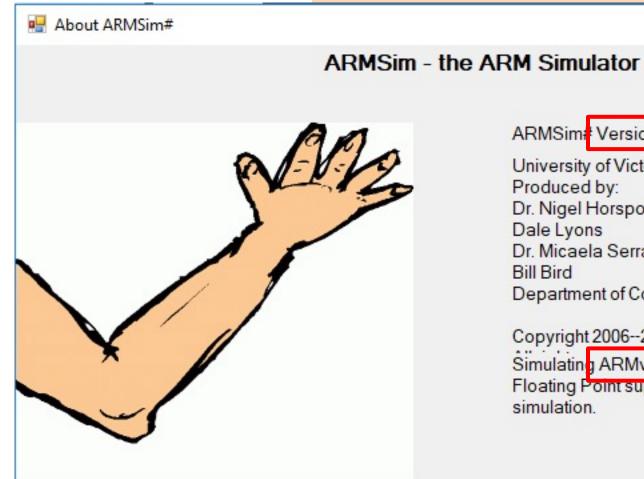

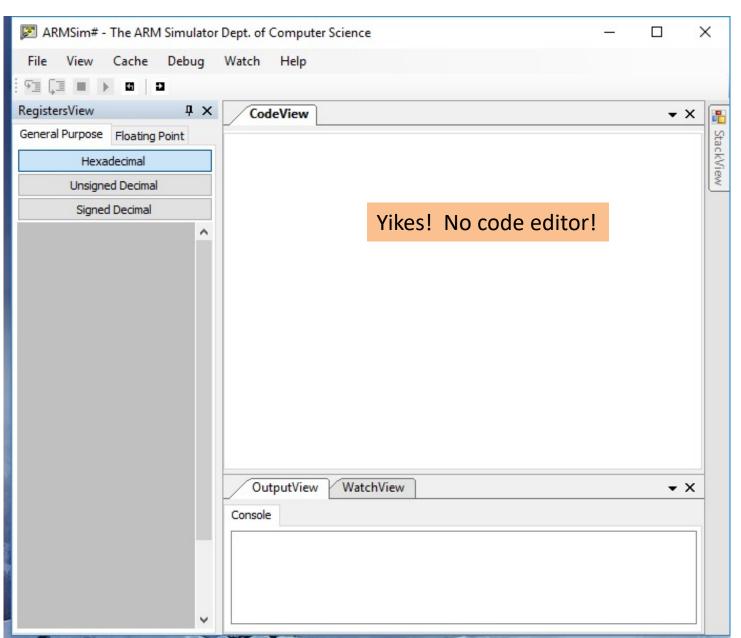

- ❖SDK/IDE: ARMsim → slide 78

- ♦ Assembly → slide 92

- ❖Instruction Set → slide 131

- ♦ Website: coranac → slide 137

- ❖ARM Ref Man Intro → slide 144

- ❖ARM RM Instr Set → slide 159

Legend

CPU design

Company

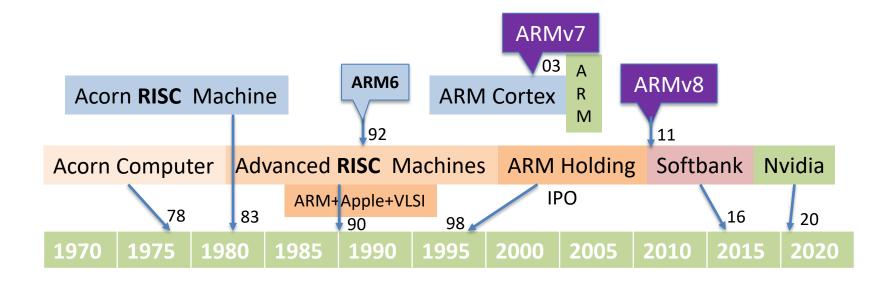

The Acorn Archimedes is a family of personal computers designed by Acorn Computers of Cambridge, England. The systems were based on Acorn's own ARM architecture processors and the proprietary operating systems Arthur and RISC OS. The first models were introduced in 198

Arm (previously officially written all caps as ARM and usually written as such today), previously Advanced RISC Machine, originally Acorn RISC Machine, is a family of reduced instruction set computing (RISC) architectures for computer processors, configured for various environments. Arm Holdings develops the architecture and licenses it to other companies, who design their own products that implement one of those architectures—including systems-on-chips (SoC) and systems-on-modules (SoM) that incorporate memory, interfaces, radios, etc. It also designs cores that implement this instruction set and licenses these designs to a number of companies that incorporate those core designs into their own products.

Processors that have a RISC architecture typically require fewer transistors than those with a complex instruction set computing (CISC) architecture (such as the x86 processors found in most personal computers), which improves cost, power consumption, and heat dissipation. These characteristics are desirable for light, portable, battery-powered devices—including smartphones, laptops and tablet computers, and other embedded systems<sup>[3][4][5]</sup>—but are also useful for servers and desktops to some degree. For supercomputers, which consume large amounts of electricity, Arm is also a power-efficient solution.<sup>[6]</sup>

ARM

1990 joint venture

Cambridge-based Arm Ltd was founded in 1990 as a joint venture between Apple, Acorn Computers and VLSI Technology. It designs software and semiconductors – components of electrical circuits that are used to manage the flow of current.

It is not just the UK's largest tech company but a genuine global powerhouse that has, in the space of 30 years, grown into a \$40bn (£31bn) business with more than 6,000 employees.

## What's so great about it?

Its semiconductor chips are the building blocks of a string of consumer favourites. Apple uses them in its iPhone, iPad and Apple Watch products, but you'll also find Arm chips in the Playstation Vita and Nintendo DS and Wii gaming devices and Garmin satnavs, as well as Sony Ericsson and Samsung Galaxy phones. Its chips are increasingly used in the rapidly-expanding web of connected devices known as the "internet of things".

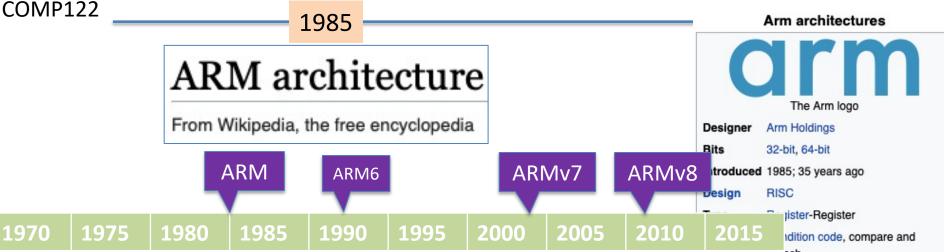

#### ARM architecture

From Wikipedia, the free encyclopedia

Acorn RISC Machine

#### Name [edit]

The acronym ARM was first used in 1983 and originally stood for "Acorn RISC Machine". Acorn Computers' first RISC processor was used in the original Acorn Archimedes and was one of the first RISC processors used in small computers. However, when the company was incorporated in 1990, what 'ARM' stood for changed to "Advanced RISC Machines", in light of the company's name "Advanced RISC Machines Ltd." – and according to an interview with Steve Furber the name change was also at the behest of Apple, which did not wish to have the name of a former competitor – namely Acorn – in the name of the company. At the time of the IPO in 1998, the company name was changed to "ARM Holdings", [18] often just called ARM like the processors.

On 1 August 2017, the styling and logo were changed. The logo is now all lowercase ('arm') and other uses of the name are in sentence case ('Arm') except where the whole sentence is upper case, so, for instance, it became 'Arm Holdings', [19] and since only Arm Ltd.

#### Founding [edit]

The company was founded in November 1990 as **Advanced RISC Machines Ltd** and structured as a joint venture between Acorn Computers, Apple, and VLSI Technology. Acorn provided 12 employees, VLSI provided tools, Apple provided \$3 million investment. [20][21] Larry Tesler, Apple VP was a key person and the first CEO at the joint venture. [22][23] The new company intended to further the development of the Acorn RISC Machine processor, which was originally used in the Acorn Archimedes and had been selected by Apple for its Newton project. Its first profitable year was 1993. The company's Silicon Valley and Tokyo offices were opened in 1994. ARM invested in Palmchip Corporation in 1997 to provide system on chip platforms and to enter into the disk drive market. [24][25] In 1998, the company changed its name from *Advanced RISC Machines Ltd* to *ARM Ltd*. [26] The company was first listed on the London Stock Exchange and NASDAQ in 1998[27] and by February 1999, Apple's shareholding had fallen to 14.8%. [28]

In 2010, ARM joined with IBM, Texas Instruments, Samsung, ST-Ericsson (since dissolved) and Freescale Semiconductor (now NXP Semiconductors) in forming a non-profit open source engineering company, Linaro.<sup>[29]</sup>

#### ARM architecture

From Wikipedia, the free encyclopedia

#### Advanced RISC Machines Ltd. – ARM6 [edit]

In the late 1980s, Apple Computer and VLSI Technology started working with Acorn on newer versions of the ARM core. In 1990, Acorn spun off the design team into a new company named Advanced RISC Machines Ltd., [43][44][45] which became ARM Ltd. when its parent company, Arm Holdings plc, floated on the London Stock Exchange and NASDAQ in 1998. [46] The new Apple-ARM work would eventually evolve into the ARM6, first released in early 1992. Apple used the ARM6-based ARM610 as the basis for their Apple Newton PDA.

There have been several generations of the ARM design. The original ARM1 used a 32-bit internal structure but had a 26-bit address space that limited it to 64 MB of main memory. This limitation was removed in the ARMv3 series, which has a 32-bit address space, and several additional generations up to ARMv7 remained 32-bit. Released in 2011, the ARMv8-A architecture added support for a 64-bit address space and 64-bit arithmetic with its new 32-bit fixed-length instruction set.<sup>[3]</sup> Arm Ltd. has also released a series of additional instruction sets for different rules; the "Thumb" extension adds both 32- and 16-bit instructions for improved code density, while Jazelle added instructions for directly handling Java bytecodes, and more recently, JavaScript. More recent changes include the addition of simultaneous multithreading (SMT) for improved performance or fault tolerance.<sup>[4]</sup>

ARM architecture

From Wikipedia, the free encyclopedia

**UCB Prof David Patterson**

#### Design concepts [edit]

The original Berkeley RISC designs were in some sense teaching systems, not designed specifically for outright performance. To its basic register-heavy concept, ARM added a number of the well-received design notes of the 6502. Primary among them was the ability to quickly serve interrupts, which allowed the machines to offer reasonable input/output performance without any additional external hardware. To offer similar high-performance interrupts as the 6502, the ARM design limited its physical address space to 24 bits with 4-byte word addressing, so 26 bits with byte addressing, or 64 MB. As all ARM instructions are aligned on word boundaries, so that an instruction address is a word address, the program counter (PC) thus only needed to be 24 bits. This 24-bit size allowed the PC to be stored along with eight processor flags in a single 32-bit register. That meant that on the reception of an interrupt, the entire machine state could be saved in a single operation, whereas had the PC been a full 32-bit value, it would require separate operations to store the PC and the status flags.<sup>[30]</sup>

Another change, and among the most important in terms of practical real-world performance, was the modification of the instruction set to take advantage of page mode DRAM. Recently introduced, page mode allowed subsequent accesses of memory to run twice as fast if they were roughly in the same location, or "page". Berkeley's design did not consider page mode, and treated all memory equally. The ARM design added special vector-like memory access instructions, the "S-cycles", that could be used to fill or save multiple registers in a single page using page mode. This doubled memory performance when they could be used and was especially important for graphics performance.<sup>[31]</sup>

The Berkeley RISC designs used register windows to reduce the number of register saves and restores performed in procedure calls; the ARM design did not adopt this.

Wilson developed the instruction set, writing a simulation of the processor in BBC BASIC that ran on a BBC Micro with a second 6502 processor.<sup>[32][33]</sup> This convinced Acorn engineers they were on the right track. Wilson approached Acorn's CEO, Hermann Hauser, and requested more resources. Hauser gave his approval and assembled a small team to design the actual processor based on Wilson's ISA.<sup>[34]</sup> The official Acorn RISC Machine project started in October 1983.

AN ARM AND

A LEG

**BIOTECH**

BOOST

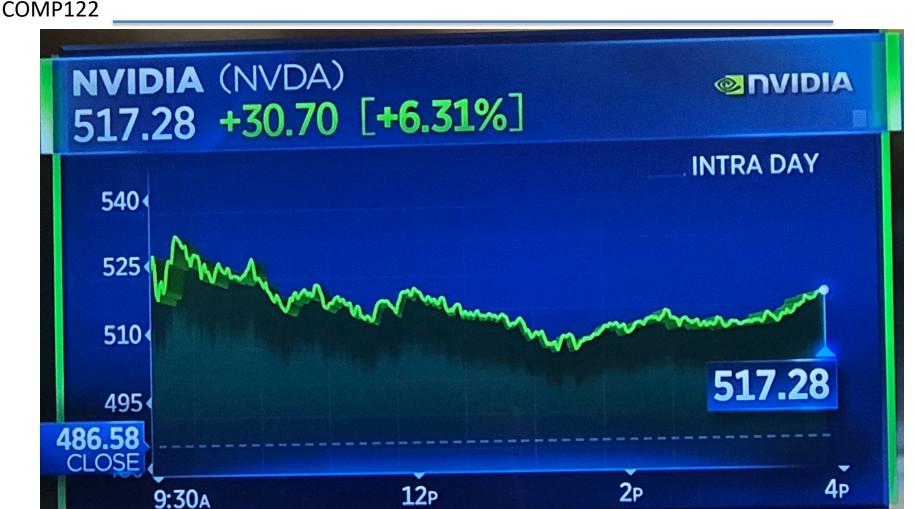

# Nvidia Buys ARM

INTO THE CLOSE

MARKET

**NVIDIA TO BUY ARM HOLDINGS FOR \$40B**

**WANNA BET?**

# Nvidia Buys ARM

\$40B

COMP122

What will be the ramifications on ARM's business if NVIDIA acquires ARM from SoftBank?

Jeff Drobman · just now

Lecturer at California State University, Northridge (2016-present)

my guess is that the DOJ will lay a heavy hand (or arm) on this deal: permitting it only if Nvidia agrees to an "arm's-length" (puns intended) management. Nvidia will likely have to agree to continue licensing its many core designs and ISA's, especially ARMv7 and ARMv8.

Actually the UK equiv

➤ Japanese conglomerate Softbank bought ARM Holdings in 2016 for \$32B

### What does Nvidia say?

Nvidia boss Huang has sought to allay such fears, promising to keep the Arm brand and expand its Cambridge HQ.

"We will expand on this great site and build a world-class artificial intelligence research facility, supporting developments in healthcare, life sciences, robotics, self-driving cars and other fields," he said.

ΑI

# Nvidia + ARM

NORTHRIDGE INVICIA T MINIVI

# **ARM CPU Models**

- Timeline of models

- ❖ Apple A series (A12-15)

- New models

- CPU: Cortex A-78

- GPU: Mali

- NPU: Ethos

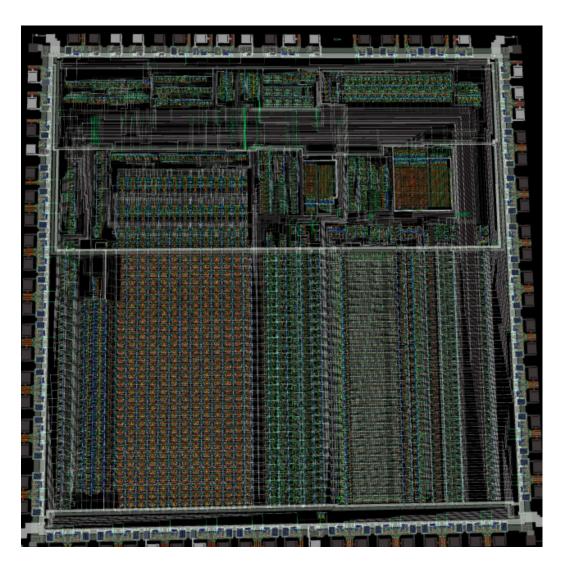

# ARM 1 Die Sim

http://visual6502.org/sim/varm/armgl.html

Mousewheel or Z,X keys: zoom Left-drag: rotate W,A,S,D: pan

cycle:77 phi2:0 A:00000050 D:0f000000 r r15(pc):00000034 (USR) nzcvifss r0:0f000000 Hz: 3.7

phi1 phi2 ale abe dbe abrt irq firq

1 0 1 1 1 0 1 1

reset seq m0 m1 bw rw opc mreq tran

0 0 1 1 1 1 1 0 0

r15 (pc) r14 (link) r13 r12 00000034 ffffffff ffffffff ffffffff r11 r10 r9 r8 ffffffff ffffffff ffffffff ffffffff r7 r6 r5 r4 ffffffff ffffffff ffffffff ffffffff r2 r3r1r0 00000050 00000009 0000000f 0f000000 r14\_svc r13\_svc 00000028 ffffffff r14\_irq r13\_irq r10\_fiq ffffffff ffffffff ffffffff r14 fiq r13 fiq r12 fiq r11 fiq ffffffff fffffff ffffffff ffffffff

Downloads complete, version 019

© <u>Visual6502.org</u>

ARM1 geometry provided under EULA with <u>ARM</u>

## **ARM CPUs**

| CPU | Fam | ily |

|-----|-----|-----|

|     |     | /   |

X Cortex-A

Supreme performance at optimal power

Cortex-R

Reliable mission-critical performance

Cortex-M

Powering the most energy-efficient embedded devices

8/16-bit **MCU**

Cortex-A:

**❖** A5

**❖** A7

**\*** A9

**❖** A15

**♦** A17

**❖** A32

**❖** A34

**❖** A35

**4** A53

**♦** A55

**♦** A57

**❖** A65

**❖** A65AE

**❖** A72

**❖** A73

**❖** A75

**❖** A76AE

**❖** A76

**❖** A77

# ARM64/ARMv8

AArch64 or ARM64 is the 64-bit extension of the ARM architecture.

## ARM vs x86 re RISC

#### Jerry Coffin

7h ago

ARM is a RINO: RISC In Name Only. It's not really significantly more RISC than modern x86, and less "RISC" than (for one obvious example) the PDP-11.

Windows NT started out on MIPS, and was later ported to x86, PowerPC, and Alpha. Much more recently, Microsoft ported Windows to ARM. So no, MIPS, Alph ... (more)

#### Jeff Drobman <

Just now

biggest feature of RISC is single-cycle instruction execution, with scalable clock frequency due to deep pipelining, next comes a large set of general registers, which x86 never had. the more registers, the less need for D-cache. ARM has these qualities, even though ARMv7 was a bit too complex with all instructions being conditional (leaves pipeline bubbles). MIPS has essentially evolved into RISC V under Prof. Patterson.

# ARM Cores 7-11 Timeline

ARM core timeline [edit]

The following table lists each core by the year it was announced. [89][90] Cores before ARM7 aren't included in this table.

| Year |                               |        | Classic c                       | Cortex cores         |                                  |                 |           |                  |

|------|-------------------------------|--------|---------------------------------|----------------------|----------------------------------|-----------------|-----------|------------------|

|      | ARM7                          | ARM8   | ARM9                            | ARM10                | ARM11                            | Microcontroller | Real-time | Applica<br>(32-b |

| 1993 | ARM700                        |        |                                 |                      |                                  |                 |           |                  |

| 1994 | ARM710<br>ARM7DI<br>ARM7TDMI  |        |                                 |                      |                                  |                 |           |                  |

| 1995 | ARM710a                       |        |                                 |                      |                                  |                 |           |                  |

| 1996 |                               | ARM810 |                                 |                      |                                  |                 |           |                  |

| 1997 | ARM710T<br>ARM720T<br>ARM740T |        |                                 |                      |                                  |                 |           |                  |

| 1998 |                               |        | ARM9TDMI<br>ARM940T             |                      |                                  |                 |           |                  |

| 1999 |                               |        | ARM9E-S<br>ARM966E-S            |                      |                                  |                 |           |                  |

| 2000 |                               |        | ARM920T<br>ARM922T<br>ARM946E-S | ARM1020T             |                                  |                 |           |                  |

| 2001 | ARM7TDMI-S<br>ARM7EJ-S        |        | ARM9EJ-S<br>ARM926EJ-S          | ARM1020E<br>ARM1022E |                                  |                 |           |                  |

| 2002 |                               |        |                                 | ARM1026EJ-S          | ARM1136J(F)-S                    |                 |           |                  |

| 2003 |                               |        | ARM968E-S                       |                      | ARM1156T2(F)-S<br>ARM1176JZ(F)-S |                 |           |                  |

| 2004 |                               |        |                                 |                      |                                  | Cortex-M3       |           |                  |

# ARM Cores 7-11 Timeline

| 2005 |    |         | ARM11MPCore |                             |                                     | Cortex-A8  |                                            |                            |

|------|----|---------|-------------|-----------------------------|-------------------------------------|------------|--------------------------------------------|----------------------------|

| 2006 | AF | RM996HS |             |                             |                                     |            |                                            |                            |

| 2007 |    |         |             | Cortex-M1                   |                                     | Cortex-A9  |                                            |                            |

| 2008 |    |         |             |                             |                                     |            |                                            |                            |

| 2009 |    |         |             | Cortex-M0                   |                                     | Cortex-A5  |                                            |                            |

| 2010 |    |         |             | Cortex-M4(F)                |                                     | Cortex-A15 |                                            |                            |

| 2011 |    |         |             |                             | Cortex-R4<br>Cortex-R5<br>Cortex-R7 | Cortex-A7  |                                            |                            |

| 2012 |    |         |             | Cortex-M0+                  |                                     |            | Cortex-A53<br>Cortex-A57                   |                            |

| 2013 |    |         |             |                             |                                     | Cortex-A12 |                                            |                            |

| 2014 |    |         |             | Cortex-M7(F)                |                                     | Cortex-A17 |                                            |                            |

| 2015 |    |         |             |                             |                                     |            | Cortex-A35<br>Cortex-A72                   |                            |

| 2016 |    |         |             | Cortex-M23<br>Cortex-M33(F) | Cortex-R8<br>Cortex-R52             | Cortex-A32 | Cortex-A73                                 |                            |

| 2017 |    |         |             |                             |                                     |            | Cortex-A55<br>Cortex-A75                   |                            |

| 2018 |    |         |             | Cortex-M35P(F)              |                                     |            | Cortex-A65AE<br>Cortex-A76<br>Cortex-A76AE |                            |

| 2019 |    |         |             |                             |                                     |            | Cortex-A77                                 | Neoverse E1<br>Neoverse N1 |

| 2020 |    |         |             | Cortex-M55(F)               | Cortex-R82                          |            | Cortex-A78<br>Cortex-X1 <sup>[91]</sup>    |                            |

# ARM Timeline (v1-7)

| ISA             | Core            | Cores                                                                                                            |                                                     |  |  |

|-----------------|-----------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|--|

| Architecture \$ | bit- +<br>width | Arm Holdings \$                                                                                                  | Third-party \$                                      |  |  |

| Armv1           | 32              | ARM1                                                                                                             |                                                     |  |  |

| Armv2           | 32              | ARM2, Arm250, ARM3                                                                                               | Amber, STORM Open Soft Core <sup>[47]</sup>         |  |  |

| Armv3           | 32              | ARM6, ARM7                                                                                                       |                                                     |  |  |

| Armv4           | 32              | Arm8                                                                                                             | StrongARM, FA526, ZAP Open Source Processor<br>Core |  |  |

| Armv4T          | 32              | ARM7TDMI, ARM9TDMI, SecurCore SC100                                                                              |                                                     |  |  |

| Armv5TE         | 32              | ARM7EJ, ARM9E, ARM10E                                                                                            | XScale, FA626TE, Feroceon, PJ1/Mohawk               |  |  |

| Armv6           | 32              | ARM11                                                                                                            |                                                     |  |  |

| Armv6-M         | 32              | Arm Cortex-M0, ARM Cortex-M0+, ARM Cortex-M1, SecurCore SC000                                                    |                                                     |  |  |

| Armv7-M         | 32              | Arm Cortex-M3, SecurCore SC300                                                                                   |                                                     |  |  |

| Armv7E-M        | 32              | Arm Cortex-M4, ARM Cortex-M7                                                                                     |                                                     |  |  |

| Armv8-M         | 32              | Arm Cortex-M23, <sup>[49]</sup> Arm Cortex-M33 <sup>[50]</sup>                                                   |                                                     |  |  |

| Armv7-R         | 32              | ARM Cortex-R4, ARM Cortex-R5,<br>ARM Cortex-R7, ARM Cortex-R8                                                    |                                                     |  |  |

| Armv8-R         | 32              | ARM Cortex-R52                                                                                                   |                                                     |  |  |

| Armv7-A         | 32              | ARM Cortex-A5, ARM Cortex-A7, ARM Cortex-A8,<br>ARM Cortex-A9, ARM Cortex-A12,<br>ARM Cortex-A15, ARM Cortex-A17 | Qualcomm Scorpion/Krait, PJ4/Sheeva, Apple<br>Swift |  |  |

# ARM Timeline (v8)

| ARMv8-A   | 32    | ARM Cortex-A32 <sup>[54]</sup>                                                                                                                                                                                                    |                                                                                                                                                                                                     |

|-----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 64/32 | ARM Cortex-A35, <sup>[55]</sup> ARM Cortex-A53,<br>ARM Cortex-A57, <sup>[56]</sup> ARM Cortex-A72, <sup>[57]</sup><br>ARM Cortex-A73 <sup>[58]</sup>                                                                              | X-Gene, Nvidia Denver 1/2, Cavium ThunderX, AMD K12, Apple Cyclone (A7)/Typhoon (A8, A8X)/Twister (A9, A9X)/Hurricane+Zephyr (A10, A10X), Qualcomm Kryo, Samsung M1/M2 ("Mongoose") /M3 ("Meerkat") |

|           | 64    | ARM Cortex-A34 <sup>[65]</sup>                                                                                                                                                                                                    |                                                                                                                                                                                                     |

| ARMv8.1-A | 64/32 | TBA                                                                                                                                                                                                                               | Cavium ThunderX2                                                                                                                                                                                    |

|           | 64/32 | ARM Cortex-A55, <sup>[67]</sup> ARM Cortex-A75, <sup>[68]</sup> ARM Cortex-A76, <sup>[69]</sup> ARM Cortex-A77, ARM Cortex-A78, ARM Cortex-X1, ARM Neoverse N1                                                                    | Nvidia Carmel, Samsung M4 ("Cheetah"),<br>Fujitsu A64FX (ARMv8 SVE 512-bit)                                                                                                                         |

| ARMv8.2-A | 64    | ARM Cortex-A65, ARM Neoverse E1 with simultaneous multithreading (SMT), ARM Cortex-A65AE <sup>[73]</sup> (also having e.g. ARMv8.4 Dot Product; made for safety critical tasks such as advanced driver-assistance systems (ADAS)) | Apple Monsoon+Mistral (A11) (September 2017)                                                                                                                                                        |

|           | 64/32 | TBA                                                                                                                                                                                                                               |                                                                                                                                                                                                     |

| ARMv8.3-A | 64    | ТВА                                                                                                                                                                                                                               | Apple Vortex+Tempest (A12, A12X, A12Z),<br>Marvell ThunderX3 (v8.3+) <sup>[74]</sup>                                                                                                                |

| ADM:04 A  | 64/32 | TBA                                                                                                                                                                                                                               |                                                                                                                                                                                                     |

| ARMv8.4-A | 64    | TBA                                                                                                                                                                                                                               | Apple Lightning+Thunder (A13)                                                                                                                                                                       |

| ARMv8.5-A | 64/32 | ТВА                                                                                                                                                                                                                               |                                                                                                                                                                                                     |

| ARMv8.6-A | 64    | TBA                                                                                                                                                                                                                               | Apple Firestorm+Icestorm (A14, M1)                                                                                                                                                                  |

# ARM 3<sup>rd</sup> Party SoC

|                              |           | I                                     |                                                                                                                                                      |                                                                                    | 7                                    |

|------------------------------|-----------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------|

| X-Gene<br>(Applied<br>Micro) | ARMv8-A   | X-Gene                                | 64-bit, quad issue, SMP, 64 cores <sup>[81]</sup>                                                                                                    | Cache, MMU, virtualization                                                         | 3 GHz (4.2<br>DMIPS/MHz per<br>core) |

| Denver<br>(Nvidia)           | ARMv8-A   | Denver <sup>[82][83]</sup>            | 2 cores. AArch64, 7-wide superscalar, in-order, dynamic code optimization, 128 MB optimization cache,  Denver1: 28nm, Denver2:16nm                   | 128 KB I-cache / 64 KB D-cache                                                     | Up to 2.5 GHz                        |

| Carmel<br>(Nvidia)           | ARMv8.2-A | Carmel <sup>[84][85]</sup>            | 2 cores. AArch64, 10-wide superscalar, in-order, dynamic code optimization, ? MB optimization cache, functional safety, dual execution, parity & ECC | ? KB I-cache / ? KB D-cache                                                        | Up to ? GHz                          |

| ThunderX<br>(Cavium)         | ARMv8-A   | ThunderX                              | 64-bit, with two models with 8–16 or 24–48 cores (x2 w/two chips)                                                                                    | ?                                                                                  | Up to 2.2 GHz                        |

| K12<br>(AMD)                 | ARMv8-A   | K12 <sup>[86]</sup>                   | ?                                                                                                                                                    | ?                                                                                  | ?                                    |

|                              | ARMv8-A   | M1/M2<br>("Mongoose") <sup>[87]</sup> | 4 cores. AArch64, 4-wide, quad-issue, superscalar, out-of-<br>order                                                                                  | 64 KB I-cache / 32 KB D-cache, L2: 16-<br>way shared 2 MB                          | 5.1 DMIPS/MHz<br>(2.6 GHz)           |

| Exynos<br>(Samsung)          | ARMv8-A   | M3 ("Meerkat")[88]                    | 4 cores, AArch64, 6-decode, 6-issue, 6-wide. superscalar, out-of-order                                                                               | 64 KB I-cache / 32 KB D-cache, L2: 8-way<br>private 512 KB, L3: 16-way shared 4 MB | ?                                    |

|                              | ARMv8.2-A | M4 ("Cheetah")                        | 2 cores, AArch64, 6-decode, 6-issue, 6-wide. superscalar, out-of-order                                                                               | 64 KB I-cache / 32 KB D-cache, L2: 8-way<br>private 512 KB, L3: 16-way shared 4 MB | ?                                    |

# CALIFORNIA STATE UNIVERSITY NORTHRIDGE ARM Soc — Apple, Qualcomm COMP122

|                          | ARMv7-A   | Scorpion <sup>[71]</sup>                 | 1 or 2 cores. ARM / Thumb / Thumb-2 / DSP / SIMD / VFPv3 FPU / NEON (128-bit wide)                                                                                   | 256 KB L2 per core                                       | 2.1 DMIPS/MHz<br>per core           |

|--------------------------|-----------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------|

| Snapdragon<br>(Qualcomm) | ARIVIV7-A | Krait <sup>[71]</sup>                    | 1, 2, or 4 cores. ARM / Thumb / Thumb-2 / DSP / SIMD / VFPv4 FPU / NEON (128-bit wide)                                                                               | 4 KB / 4 KB L0, 16 KB / 16 KB L1, 512 KB<br>L2 per core  | 3.3 DMIPS/MHz<br>per core           |

|                          | ARMv8-A   | Kryo <sup>[72]</sup>                     | 4 cores.                                                                                                                                                             | ?                                                        | Up to 2.2 GHz<br>(6.3<br>DMIPS/MHz) |

|                          | ARMv7-A   | Swift <sup>[73]</sup>                    | 2 cores. ARM / Thumb / Thumb-2 / DSP / SIMD / VFPv4 FPU / NEON                                                                                                       | L1: 32 KB / 32 KB, L2: 1 MB                              | 3.5 DMIPS/MHz<br>per core           |

|                          | ARMv8-A   | Cyclone <sup>[74]</sup>                  | 2 cores. ARM / Thumb / Thumb-2 / DSP / SIMD / VFPv4 FPU / NEON / TrustZone / AArch64. Out-of-order, superscalar.                                                     | L1: 64 KB / 64 KB, L2: 1 MB, L3: 4 MB                    | 1.3 or 1.4 GHz                      |

| Ax<br>(Apple)            | ARMv8-A   | Typhoon <sup>[74][75]</sup>              | 2 or 3 cores. ARM / Thumb / Thumb-2 / DSP / SIMD / VFPv4<br>FPU / NEON / TrustZone / AArch64                                                                         | L1: 64 KB / 64 KB, L2: 1 MB or 2 MB, L3:<br>4 MB         | 1.4 or 1.5 GHz                      |

|                          | ARMv8-A   | Twister <sup>[76]</sup>                  | 2 cores. ARM / Thumb / Thumb-2 / DSP / SIMD / VFPv4 FPU / NEON / TrustZone / AArch64                                                                                 | L1: 64 KB / 64 KB, L2: 2 MB, L3: 4 MB or<br>0 MB         | 1.85 or 2.26 GHz                    |

|                          | ARMv8.1-A | Hurricane and<br>Zephyr <sup>[77]</sup>  | Hurricane: 2 or 3 cores. AArch64, 6-decode, 6-issue, 9-wide, superscalar, out-of-order Zephyr: 2 or 3 cores. AArch64.                                                | L1: 64 KB / 64 KB, L2: 3 MB or 8 MB, L3:<br>4 MB or 0 MB | 2.34 or 2.38 GHz                    |

|                          | ARMv8.2-A | Monsoon and<br>Mistral <sup>[78]</sup>   | Monsoon: 2 cores. AArch64, 7-decode, ?-issue, 11-wide, superscalar, out-of-order  Mistral: 4 cores. AArch64, out-of-order, superscalar. Based on Swift.              | L1I: 128 KB, L1D: 64 KB, L2: 8 MB, L3:<br>4 MB           | 2.39 GHz                            |

|                          | ARMv8.3-A | Vortex and<br>Tempest <sup>[79]</sup>    | Vortex: 2 or 4 cores. AArch64, 7-decode, ?-issue, 11-wide, superscalar, out-of-order Tempest: 4 cores. AArch64, 3-decode, out-of-order, superscalar. Based on Swift. | L1: 128 KB / 128 KB, L2: 8 MB, L3: 8 MB                  | 2.5 GHz                             |

|                          | ARMv8.4-A | Lightning and<br>Thunder <sup>[80]</sup> | Lightning: 2 cores. AArch64, 7-decode, ?-issue, 11-wide, superscalar, out-of-order Thunder: 4 cores. AArch64, out-of-order, superscalar.                             | L1: 128 KB / 128 KB, L2: 8 MB, L3: 16 MB                 | 2.66 GHz                            |

#### Cortex-A75

First DynamlQ-based high performance CPU

- Flexible architecture provides a broad ecosystem of support

- Executes up to three instructions in parallel per clock cycle

- Broad market use covers smartphones, servers, automotive applications and more

#### Cortex-A73

Most power-efficient processor in the Cortex-A family

- Increased power efficiency of up to 30 percent over predecessors

- Smallest Armv8-A processor

- Designed for mobile and consumer applications

#### Cortex-A72

Fast processing improves the efficiency of mobile applications

- Advanced branch predictor reduces wasted energy consumption

- Gain significant advantages in reduced memory requirements

- Suitable for implementation in an Arm big.LITTLE configuration

## **Features and Benefits**

# High Compute Density

Gain significant advantages in reduced memory requirements and maximizing the use of on-chip Flash memory with advanced code density.

## Advanced Branch Predictor

Drastically improve prediction accuracy with a sophisticated new algorithm, which reduces wasted energy consumption from executing down an incorrect code path.

# Infrastructure Compatibility

Develop more advanced networking and storage applications by harnessing the full error-correcting code cache and 44-bit addressing up to 16TB.

# Processing Architecture for Power Efficiency and Performance

Arm big.LITTLE technology is a heterogeneous processing architecture that uses two types of processor. "LITTLE" processors are designed for maximum power efficiency while "big" processors are designed to provide maximum compute performance. With two dedicated processors, the big.LITTLE solution is able to adjust to the dynamic usage pattern for smartphones, tablets and other devices. Big.LITTLE adjusts to periods of high-processing intensity, such as those seen in mobile gaming and web browsing, alternate with typically longer periods of low-processing intensity tasks such as texting, e-mail and audio, and quiescent periods during complex apps.

The performance demanded from users of current smartphones and tablets is increasing at a much faster rate than the capacity of batteries or power savings from advances in semiconductor process. At the same time, users are demanding longer battery life within roughly the same form factor. This conflicting set of demands requires innovations in mobile SoC design beyond what process technology and traditional power management techniques can deliver.

#### Armv8

- High-performance CPU (big): Cortex-A73, Cortex-A75, Cortex-A76

- High-efficiency CPU (LITTLE): Cortex-A53, Cortex-A55

## **Features and Benefits**

# Heterogenous Solution

Arm big.LITTLE processing takes advantage of the variation smart devices require in performance by combining two very different processors together in a single SoC.

## Maximum Performance

The big processor is designed for maximum performance within the mobile power budget.

## Optimal Energyeffiency

The smaller processor is designed for optimal efficiency and is capable of addressing all but the most intense periods of work.

#### **Typical Processor Combinations**

Arm Cortex-A series processor combinations that meet big.LITTLE requirements are shown below

#### Armv8

- High-performance CPU (big): Cortex-A73, Cortex-A75, Cortex-A76

- High-efficiency CPU (LITTLE): Cortex-A53, Cortex-A55

Yowan Rajcoomar, Computer Technician (2008-present)

Answered 7h ago

The 'Efficiency' cores can also be considered as high end since they are superscalar out of order designs with speculative execution unlike ARM's reference efficiency cores like the Cortex-A53 and A55.

In fact, they're as complex as ARM's older high end A75 cores. Quoting AnandTech:

What we didn't cover in more detail in the M1 piece was the new small efficiency cores. The Icestorm design is actually a quite major leap for Apple as it sees the introduction of a third integer ALU pipeline, and a full second FP/SIMD pipeline, vastly increasing the execution capabilities of this core. At this point it would be wrong to call it a "small" core anymore as it now essentially matches the big core designs from Arm from a few years ago, being similar in complexity as an A75.

#### Emphasis mine.

And that's not only it. Apple's efficiency cores also manage to offer performance levels comparable to ARM's Cortex-A76 while being more efficient than the A55.

# Architecture

COMP122

Hennessy & Patterson —

Figure 4.11.1: Specification of the ARM Cortex-A53 and the Intel Core i7 920 (COD Figure 4.72).

| Processor                     | ARM A53                            | Intel Core i7 920                     |

|-------------------------------|------------------------------------|---------------------------------------|

| Market                        | Personal Mobile Device             | Server, Cloud                         |

| Thermal design power          | 100 milliWatts<br>(1 core @ 1 GHz) | 130 Watts                             |

| Clock rate                    | 1.5 GHz                            | 2.66 GHz                              |

| Cores/Chip                    | 4 (configurable)                   | 4                                     |

| Floating point?               | Yes                                | Yes                                   |

| Multiple Issue?               | Dynamic                            | Dynamic                               |

| Peak instructions/clock cycle | 2                                  | 4                                     |

| Pipeline Stages               | 8                                  | 14                                    |

| Pipeline schedule             | Static In-order                    | Dynamic Out-of-order with Speculation |

| Branch prediction             | Hybrid                             | 2-level                               |

| 1st level caches/core         | 16-64 KiB I, 16-64 KiB D           | 32 KiB I, 32 KiB D                    |

| 2nd level cache/core          | 128–2048 KiB (shared)              | 256 KiB (per core)                    |

| 3rd level cache (shared)      | (platform dependent)               | 2-8 MiB                               |

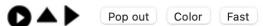

# Hardware-ARM SoC

**DR JEFF** © Jeff Drobman 2016-2022

Hennessy & Patterson

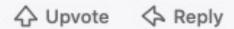

## **ARM M Series**

**MCU**

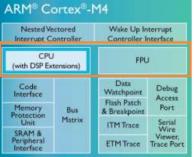

#### ARM Cortex-M Product Line

Debug

Access

ARM® Cortex®-M0+ Nested Vectored Wake Up Interrupt Interrupt Controller Controller Interface ARM® Cortex®-M0 Wake Up Interrupt Nested Vectored CPU Interrupt Controller Controller Interface Data Memory CPU Watchpoint Protection Unit Breakpoint Data AHB-lite Low Latency Debug Micro Trace Watchpoint AHB-lite Interface I/O Interface Buffer Access Interface Breakpoint Lowest power Outstanding energy efficiency

> Lowest cost Low power

Performance efficiency Feature rich connectivity

Digital Signal Control Processor with DSP Accelerated SIMD Floating point

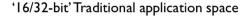

# **ARM M Series**

MCU

### ARM Cortex-M Instruction Set Architecture

Cortex-M4

Cortex-M3

Cortex-M0/M0+

# ARM M Series – MO

**COMP122**

**MCU**

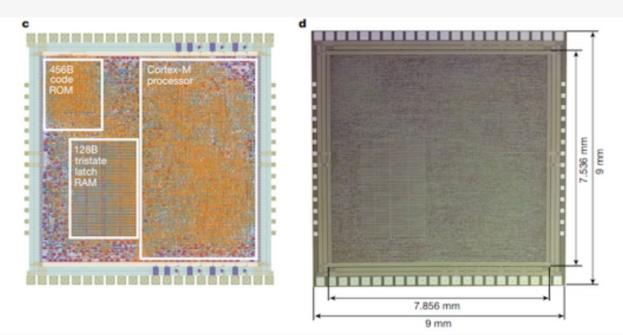

#### Details on the Plastic M0

In Arm's press release, the company states that the Plastic M0 design has 128 bytes of RAM and 456 bytes of ROM, while also supporting a 32-bit Arm microarchitecture.

Inside the research paper published at Nature, we get fine-grained details.

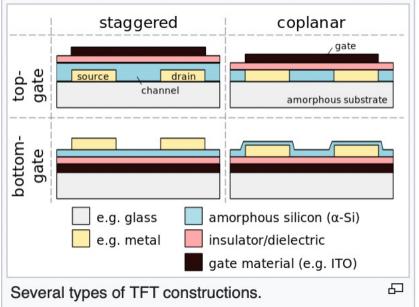

The processor is built with a polyimide substrate and is formed through thin-film metal-oxide transistors, such as IGZO TFTs. This means that this is still technically a photolithography process, using spin-coating and photoresist techniques, ending up with the processor having 13 material layers and 4 routable metal layers. However as TFT designs have been widespread since the use of IGZO displays, the cost of production is still quite low.

# **ARM M Series**

COMP122

MCU :

| Plastic               | Arm: the Plastic M0                                      | CO   |

|-----------------------|----------------------------------------------------------|------|

|                       |                                                          |      |

| Process Node          | FlexIC 800nm<br>n-type IGZO TFT<br>200nm polyimide wafer | NMOS |

| Die Size              | 59.2 mm2 (core only)<br>(7.536 mm x 7.856 mm)            |      |

| Thickness             | under 30 micron                                          |      |

| ISA                   | ARMv6-M<br>16-bit Thumb + subset of 32-bit               |      |

| Frequency             | 20-29 kilohertz                                          |      |

| Power                 | 21 milliWatts                                            |      |

| Pin Count             | 28 pins                                                  |      |

| Material Layers       | 13 layers                                                |      |

| Routable Metal Layers | 4 layers                                                 |      |

| Devices               | 56340<br>39157 n-type TFT + 17183 resisto                | rs   |

# **ARM M Series**

MCU

## Thin-film transistor

From Wikipedia, the free encyclopedia

This article is about TFT technology. For thin-film-transistor liquid-crystal display, see TFT LCD.

A **thin-film transistor** (**TFT**) is a special type of metal—oxide—semiconductor field-effect transistor (MOSFET)<sup>[1]</sup> made by depositing thin films of an active semiconductor layer as well as the dielectric layer and metallic contacts over a supporting (but non-conducting) substrate. A common substrate is glass, because the primary application of TFTs is in liquid-crystal displays (LCDs). This differs from the conventional bulk MOSFET transistor,<sup>[1]</sup> where the semiconductor material typically *is* the

substrate, such as a silicon wafer.

**MOSFET** on Glass or Plastic

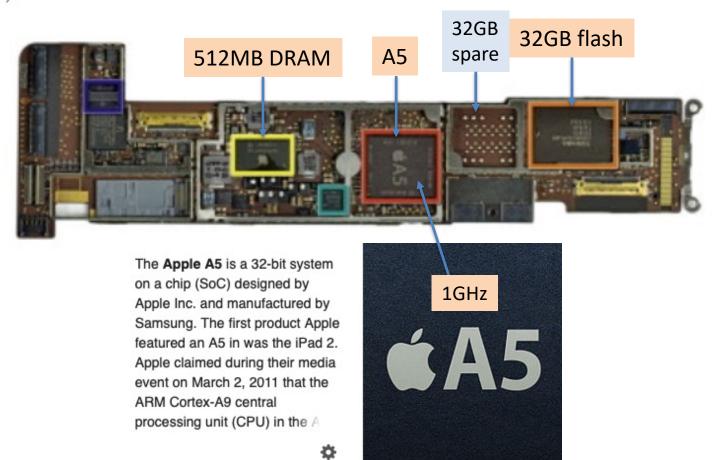

## A5 CPU on iPad2

COMP122

Hennessy & Patterson —

The logic board of Apple iPad 2 in the previous figure. The photo highlights five integrated circuits. The large integrated circuit in the middle is the Apple A5 chip, which contains dual ARM processor cores that run at 1 GHz as well as 512 MB of main memory inside the package. The next figure shows a photograph of the processor chip inside the A5 package. The similar-sized chip to the left is the 32GB flash memory chip for non-volatile storage. There is an empty space between the two chips where a second flash chip can be installed to double storage capacity of the iPad. The chips to the right of the A5 include power controller and I/O controller chips. (Courtesy iFixit, www.ifixit.com)

## Apple ARM A Series

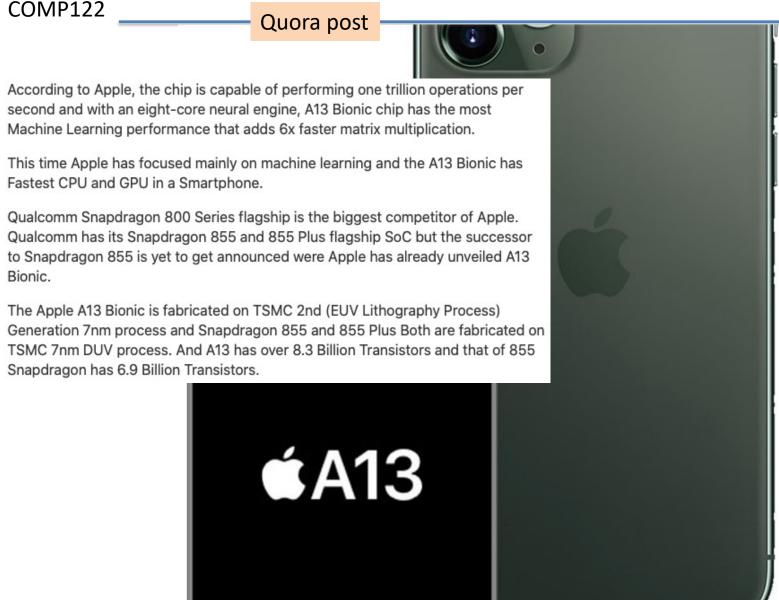

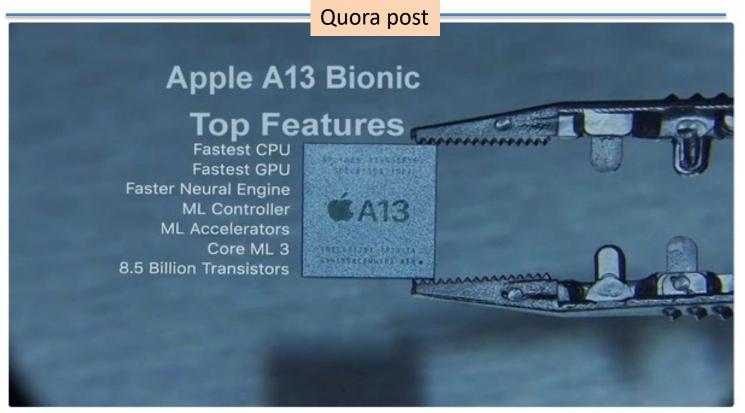

## Apple A13

In Steve Jobs Studio, Apple launched three new iPhones - iPhone 11, iPhone 11 Pro and iPhone 11 Pro Max. All these three new iPhones are based on the new Apple A13 Bionic chipset. The company launched this SoC with these iPhones. The A13 Bionic is a successor of last year's A12 Bionic SoC. The last year's A12 Bionic is ahead of Snapdragon 855 in terms of performance. According to the company, Apple A12 Bionic is at least two years ahead of other Android smartphones in the race for fast processors. After all, what is new in the A13 Bionic that makes iPhones so powerful? Don't worry, here we (more)

## Apple A13

The A13 is a new multi-core architecture designed by Apple with **8.5B** transistors manufactured at TSMC (**7nm** EUV) -- extremely state-of-the-art. It contains a large number of **ARM** ISA cores: **8 CPU + 7 GPU + 8 NPU + 2 MCU**. All cores are Apple designed (ARM 64-bit v8 ISA is licensed).

It includes a **Neural engine** (8x NPU) with machine learning (core ML 3 at 6x faster matrix multiply) – which sets it apart from Intel chips without GPU's or an NPU. The GPU's can perform 1 trillion operations per second (1 Tflops=1000 Gflops), and the NPU may hit 5 Tflops. It has extreme power management as well (so good for portables and mobile).

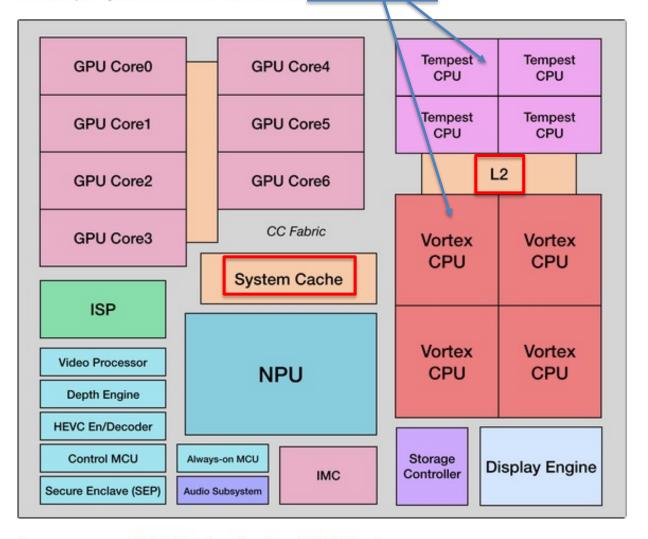

## Apple ARM A12/13 SoC

This is a block diagram of the Apple A12X with 10 billion transistors. Of that amount, only 25% is dedicated to the two CPU clusters:

- ❖ 8 CPU❖ 7 GPU

- ♣ 1 NPU

- ❖ 2 MCU

## Apple ARM A12/13 SoC

#### 3 Answers

Matthew J. Stott, Senior Systems & Mac Engineer (1996-present)

Answered Sep 30

It's called a SoC - System on Chip. It means the CPU package includes a lot more than just the CPU cores. What's changed with the A13 is even more power management abilities to shut off unused parts of the A13 but also right down to individual transistors as well. It is the most advanced power management in use right now. It is responsible for the excellent battery life of the 11, 11 Pro, 11 Pro Max iPhones. Yes, they increased the battery capacity a bit at the same time but that is just improved battery engineering.

Add to Yowan's A12X the Image Processing Core, a couple of Machine Learning accelerator cores and a bit less on the GPU with the A13 Bionic SoC. It is expected there will be an A13X for upgrade iPad Pros coming soon.

## Apple A13 v Snapdragon 855

Quora post

And I think iPhones are going to be more power-efficient than Snapdragon 855 powered Android Phones. If you are asking about CPU, then the A13 Bionic is based on 64-bit Fusion Architecture. It is a Hexa-Core CPU with 2 Performance cores and 4 Efficiency cores. And it consumes 40% less power than the A12 Bionic. Coming to 855 Snapdragon, both Snapdragon 855 and 855 Plus is an ARM 64-bit SoC with Kryo 485 Octa-Core CPU. And it has Three CPU Clusters: 1 Cortex-A76 Prime Core, 3 Cortex-A76 Performance Cores and 4 Cortex-A55 Efficiency Cores. From these it seems Snapdragon 855 will definitely be a strong competitor for the Apple A13 Bionic Chip.

Moreover, while talking about GPU, for Apple, it is an Apple-designed Quad Core GPU and Snapdragon 855 has Adreno 640 GPU. And I don't think the Snapdragon will beat the performance of Apple's A13 bionic chip.

## **New ARM Models**

## **Explore More Mobile Products**

Addresses the performance, power and cost requirements across all smartphone markets.

Mali-GPU

Provides the ultimate user experience for entertainment and visual applications across a wide range of smartphone devices.

#### Ethos-NPU

Enables new features, enhances user experiences, and delivers innovative ML-based applications on smartphones.

## New ARM Models

## New Arm IP Offers the Perfect Balance of Performance and Efficiency

Our latest mobile solution delivers performance and efficiency gains for new and improved digital immersion experiences in the 5G era.

#### Cortex-A78

The fourth-generation premium CPU based on DynamIQ technology drives innovation in mobile computing with up to 20% performance improvement on previous device generations.

#### Mali-G78

Second-generation premium

GPU based on the Mali

Valhall architecture delivers

15% improvements in

performance and efficiency

for graphic-intensive

applications.

#### Ethos-N78

Second-generation, highly scalable and efficient processor pushes the limits of mobile ML capabilities up to 10 TOPs.

The architecture capabilities of Arm's new premium IP solution and ongoing ecosystem support enables the very latest digital immersion features, including 3D rendering, depth-sensing, foldable and multiple screens, AI on device, console-like gaming and other digital world apps.

## **New ARM Models**

COMP122

"Facebook and Arm are collaborating to expand one of the most widelyused machine learning framework capabilities beyond the CPU. The combination of the Arm compute platform and PyTorch Mobile enables exciting new ML applications in edge devices."

Christian Keller, Product Manager, PyTorch Mobile

"Through our shared vision, Arm and Crytek are partnering together to bring CRYENGINE to the Android ecosystem and enable desktopclass graphics on mobile. Arm's new powerful suite of premium mobile IP is at the center of ushering in a new level of visual fidelity previously thought impossible on edge devices."

"Arm's new premium solution delivers a performant and power efficient platform that will seamlessly enable millions of Unity creators to deliver the next-generation of connected immersive experiences that will shape everyone's daily lives."

Ralph Hauwert, VP Research and Development, Unity

Theodor Mader, Technical Director CRYENGINE, Crytek

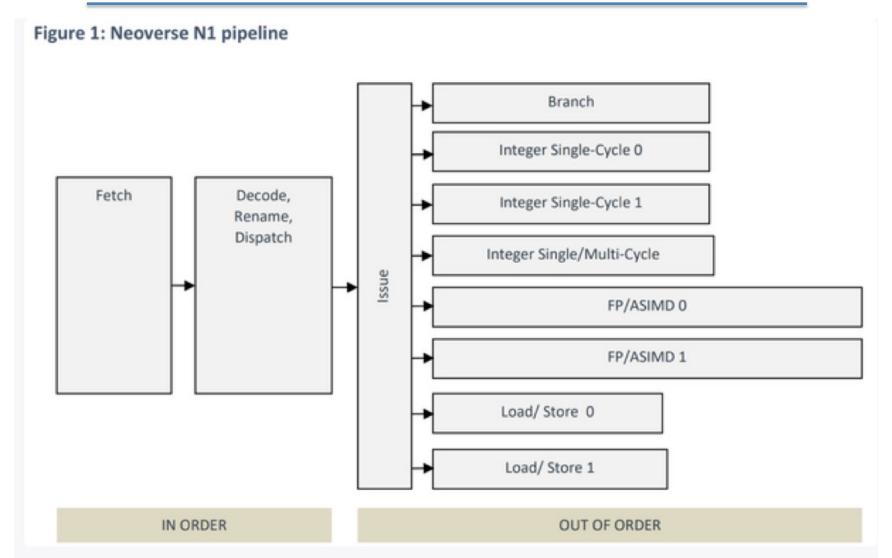

## ARM u-Arch

COMP122

The execution pipelines support different types of operations, as shown in the following table.

## ARM u-Arch

#### Table 2: Neoverse N1 operations

| Instruction groups                   | Instructions                                                                                                                              |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Branch                               | Branch μOPs                                                                                                                               |

| Integer Single-Cycle<br>0/1          | Integer ALU μOPs                                                                                                                          |

| Integer Single/Multi-<br>cycle 0/1   | Integer shift-ALU, multiply, divide, CRC and sum-of-absolute-<br>differences µOPs                                                         |

| Load/Store Address<br>Generation 0/1 | Load, Store address generation and special memory μOPs                                                                                    |

| FP/ASIMD-0                           | ASIMD ALU, ASIMD misc, ASIMD integer multiply, FP convert, FP misc, FP add, FP multiply, FP divide, FP sqrt, crypto μOPs, store data μOPs |

| FP/ASIMD-1                           | ASIMD ALU, ASIMD misc, FP misc, FP add, FP multiply, ASIMD shift μOPs, store data μOPs, crypto μOPs.                                      |

## **ARM Licensing**

**COMP122**

Companies that have developed chips with cores designed by Arm Holdings include Amazon.com's Annapurna Labs subsidiary, [41] Analog Devices, Apple, AppliedMicro (now: MACOM Technology Solutions [42]), Atmel, Broadcom, Cavium, Cypress Semiconductor, Freescale Semiconductor (now NXP Semiconductors), Huawei, Intel, [dubious – discuss] Maxim Integrated, Nvidia, NXP, Qualcomm, Renesas, Samsung Electronics, ST Microelectronics, Texas Instruments and Xilinx.

#### Built on ARM Cortex Technology licence [edit]

In February 2016, ARM announced the Built on ARM Cortex Technology licence, often shortened to Built on Cortex (BoC) licence. This licence allows companies to partner with ARM and make modifications to ARM Cortex designs. These design modifications will not be shared with other companies. These semi-custom core designs also have brand freedom, for example Kryo 280.

Companies that are current licensees of Built on ARM Cortex Technology include Qualcomm.[43]

#### Architectural licence [edit]

Companies can also obtain an ARM *architectural licence* for designing their own CPU cores using the ARM instruction sets. These cores must comply fully with the ARM architecture. Companies that have designed cores that implement an ARM architecture include Apple, AppliedMicro (now: Ampere Computing), Broadcom, Cavium (now: Marvell), Digital Equipment Corporation, Intel, Nvidia, Qualcomm, Samsung Electronics, Fujitsu and NUVIA Inc.

## **ARM Licensing**

#### ARM Flexible Access [edit]

On 16 July 2019, ARM announced ARM Flexible Access. ARM Flexible Access provides unlimited access to included ARM intellectual property (IP) for development. Per product licence fees are required once customers reaches foundry tapeout or prototyping. [44][45]

75% of ARM's most recent IP over the last two years are included in ARM Flexible Access. As of October 2019:

- CPUs: Cortex-A5, Cortex-A7, Cortex-A32, Cortex-A34, Cortex-A35, Cortex-A53, Cortex-R5, Cortex-R8, Cortex-R52, Cortex-M0, Cortex-M0+, Cortex-M3, Cortex-M4, Cortex-M7, Cortex-M23, Cortex-M33

- GPUs: Mali-G52, Mali-G31. Includes Mali Driver Development Kits (DDK).

- Interconnect: CoreLink NIC-400, CoreLink NIC-450, CoreLink CCI-400, CoreLink CCI-500, CoreLink CCI-550, ADB-400 AMBA, XHB-400 AXI-AHB

- System Controllers: CoreLink GIC-400, CoreLink GIC-500, PL192 VIC, BP141 TrustZone Memory Wrapper, CoreLink TZC-400, CoreLink L2C-310, CoreLink MMU-500, BP140 Memory Interface

- Security IP: CryptoCell-312, CryptoCell-712, TrustZone True Random Number Generator

- Peripheral Controllers: PL011 UART, PL022 SPI, PL031 RTC

- Debug & Trace: CoreSight SoC-400, CoreSight SDC-600, CoreSight STM-500, CoreSight System Trace Macrocell, CoreSight Trace Memory Controller

- . Design Kits: Corstone-101, Corstone-201

- . Physical IP: Artisan PIK for Cortex-M33 TSMC 22ULL including memory compilers, logic libraries, GPIOs and documentation

- · Tools & Materials: Socrates IP ToolingARM Design Studio, Virtual System Models

- Support: Standard ARM Technical support, ARM online training, maintenance updates, credits towards onsite training and design reviews

## ARM Mali GPU

COMP122

**GPU**

#### Mali (GPU)

From Wikipedia, the free encyclopedia

The **Mali** series of graphics processing units (GPUs) and multimedia processors are semiconductor intellectual property cores produced by ARM Holdings for licensing in various ASIC designs by ARM partners.

Mali GPUs were developed by Falanx Microsystems A/S, which was a spin-off of a research project from the Norwegian University of Science and Technology. [1] Arm Holdings acquired Falanx Microsystems A/S on June 23, 2006 and renamed the company to Arm Norway. [2]

#### Technical details [edit]

Like other embedded IP cores for 3D rendering acceleration, the Mali GPU does not include display controllers driving monitors, in contrast to common desktop video cards. Instead, the Mali ARM core is a pure 3D engine that renders graphics into memory and passes the rendered image over to another core to handle display.

ARM does, however, license display controller SIP cores independently of the Mali 3D accelerator SIP block, e.g. Mali DP500, DP550 and DP650.[3]

ARM also supplies tools to help in authoring OpenGL ES shaders named Mali GPU Shader Development Studio and Mali GPU User Interface Engine.

Display controllers such as the ARM HDLCD display controller are available separately.<sup>[4]</sup>

## Mali GPU Timeline

COMP122

**GPU**

#### Variants [edit]

The Mali core grew out of the cores previously produced by Falanx and currently constitute:

| Model <b>≑</b>      | Micro-<br>archi- \$<br>tecture | Type \$                                | Launch date \$                 | Shader<br>core \$ | Fab (nm) ÷ | Die<br>size \$<br>(mm²) | Core clock rate (MHz) | L2<br>cache + |

|---------------------|--------------------------------|----------------------------------------|--------------------------------|-------------------|------------|-------------------------|-----------------------|---------------|

| Mali-<br>55/110 &   | ?                              | Fixed function pipeline <sup>[5]</sup> | 2005 ਨੂੰ [permanent dead link] | 1                 | ?          | ?                       | ?                     | N/A           |

| Mali-<br>200 &      |                                |                                        | 2007 <sup>[8]</sup>            | 1                 | ?          | ?                       | ?                     | N/A           |

| Mali-<br>300 &      |                                | pipeline <sup>[7]</sup>                | ?                              | 1                 | 40<br>28   | ?                       | 500                   | 8 KiB         |

| Mali-400<br>MP &    | Utgard <sup>[6]</sup>          |                                        | 2008                           | 1–4               | 40<br>28   | ?                       | 200–600               | 8-256<br>KiB  |

| Mali-450<br>MP &    |                                |                                        | 2012                           | 1–8               | 40<br>28   | ?                       | 300-750               | 8-512<br>KiB  |

| Mali-470<br>MP ਔ    |                                |                                        | 2015                           | 1-4               | 40<br>28   | ?                       | 250-650               | 8–256<br>KiB  |

| Mali-<br>T604 & [9] | Midgard                        |                                        | ?                              | 1–4               | 32<br>28   | ?                       | 533                   |               |

## Mali GPU Timeline

COMP122

| Model           | Micro-<br>archi-<br>tecture    | Туре                                     | Launch date | Shader<br>core<br>count        | Fab<br>(nm)    | Die size<br>(mm²)                                             | Core<br>clock<br>rate<br>(MHz) | Max L2<br>cache<br>size |

|-----------------|--------------------------------|------------------------------------------|-------------|--------------------------------|----------------|---------------------------------------------------------------|--------------------------------|-------------------------|

| Mali-<br>G77 &  | gen                            | memory +<br>simplified<br>scalar ISA     | Q2 2019     | 7-16                           | 7              | ?                                                             | 850                            | 512–<br>4096 KiB        |

| Mali-<br>G57 &  | Valhall 1 <sup>st</sup>        | Superscalar<br>engine +<br>Unified       | Q2 2019     | 1-6                            | 7              | ?                                                             | ?                              | 64–512<br>KiB           |

| Mali-<br>G76 &  | Bifrost 3 <sup>rd</sup><br>gen |                                          | Q2 2018     | 4-20                           | 12<br>8<br>7   | ?                                                             | 600-800                        | 512-<br>4096 KiB        |

| Mali-<br>G72 &  | 1000                           |                                          | Q2 2017     | 1–32                           | 16<br>12<br>10 | 1.36 mm <sup>2</sup> per shader core at 10 nm <sup>[29]</sup> | 572-800                        | 128–<br>2048 KiB        |

| Mali-<br>G52 ਯੂ | Bifrost 2 <sup>nd</sup><br>gen | memory +<br>scalar, clause-<br>based ISA | Q1 2018     | 1-4 (2 or 3<br>EU per<br>core) | 7 16           | ?                                                             | 850                            |                         |

| Mali-<br>G71 ㎡  |                                | Unified shader<br>model +<br>Unified     | Q2 2016     | 1–32                           | 16<br>14<br>10 | ?                                                             | 546-<br>1037                   | 128–<br>2048 KiB        |

|                 |                                |                                          |             |                                |                |                                                               | GPU                            |                         |

## **ARM**

## **ARM OS**

- Embedded (RT)

- Desktop

## OS - RT

#### COMP122

The 32-bit Arm architecture is supported by a large number of embedded and real-time operating systems, including:

- A2

- Android

- ChibiOS/RT

- Deos

- DRYOS

- eCos

- embOS

- FreeRTOS

- Integrity

- Linux

- Micro-Controller Operating Systems

- MQX

- Nucleus PLUS

- NuttX

- OSE

- OS-9<sup>[139]</sup>

Android, a popular operating system which is primarily used on the Arm architecture.

- Pharos<sup>[140]</sup>

- Plan 9

- PikeOS<sup>[141]</sup>

- QNX

- RIOT

- RTEMS

- RTXC Quadros

- SCIOPTA<sup>[142]</sup>

- ThreadX

- TizenRT

- T-Kernel

- VxWorks

- · Windows Embedded Compact

- Windows 10 IoT Core

## OS – Mobile

#### Mobile device operating systems

The 32-bit Arm architecture is the p

- Android

- Bada

- BlackBerry OS/BlackBerry 10

- Chrome OS

- Firefox OS

- MeeGo

- Sailfish

- Symbian

Previously, but now discontinued:

iOS 10 and earlier

- Tizen

- Ubuntu Touch

- webOS

- Windows RT

- Windows Mobile

- Windows Phone

- Windows 10 Mobile

## OS – Desktop

#### Desktop/server operating systems [edit]

The 32-bit Arm architecture is supported by RISC OS and by multiple Unix-like operating systems including:

- FreeBSD

- NetBSD

- OpenBSD

- OpenSolaris<sup>[143]</sup>

- several Linux distributions, such as:

- Debian

- Armbian

- Gentoo

- Ubuntu

- Raspbian

- Slackware

## **ARM**

- ❖vs MIPS

- Registers

- **❖**Memory

- Instructions

COMP122

Hennessy & Patterson

#### 2.16 Real stuff: ARMv7 (32-bit) instructions

ARM is the most popular instruction set architecture for embedded devices, with more than 9 billion devices in 2011 using ARM, and recent growth has been 2 billion per year. Standing originally for the Acorn RISC Machine, later changed to Advanced RISC Machine, ARM came out the same year as MIPS and followed similar philosophies. The figure below lists the similarities. The principal difference is that MIPS has more registers and ARM has more addressing modes.

# Figure 2.16.1: Similarities in ARM and MIPS instruction sets (COD Figure 2.31).

|                                         | ARM              | MIPS             |

|-----------------------------------------|------------------|------------------|

| Date announced                          | 1985             | 1985             |

| Instruction size (bits)                 | 32               | 32               |

| Address space (size, model)             | 32 bits, flat    | 32 bits, flat    |

| Data alignment                          | Aligned          | Aligned          |

| Data addressing modes                   | 9                | 3                |

| Integer registers (number, model, size) | 15 GPR × 32 bits | 31 GPR × 32 bits |

| 1/0                                     | Memory mapped    | Memory mapped    |

COMP122

Hennessy & Patterson

# Figure 2.16.5: ARM arithmetic/logical instructions not found in MIPS (COD Figure 2.35).

| Name                                 | Definition                                                  | ARM      | MIPS      |

|--------------------------------------|-------------------------------------------------------------|----------|-----------|

| Load immediate                       | Rd = Imm                                                    | mov      | addi \$0, |

| Not                                  | ot Rd = ~(Rs1)                                              |          | nor \$0,  |

| Move                                 | Rd = Rs1                                                    | mov      | or \$0,   |

| Rotate right                         | Rd = Rs i >> i<br>Rd <sub>0i-1</sub> = Rs <sub>31-i31</sub> | ror      |           |

| And not                              | Rd = Rs1 & ~(Rs2)                                           | bic      |           |

| Reverse subtract                     | Rd = Rs2 - Rs1                                              | rsb, rsc |           |

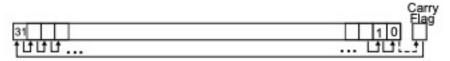

| Support for multiword<br>integer add | CarryOut, Rd = Rd + Rs1 +<br>OldCarryOut                    | adcs     | -         |

| Support for multiword<br>integer sub | CarryOut, Rd = Rd - Rs1 +<br>OldCarryOut                    | sbcs     | -         |

COMP122

Hennessy & Patterson

|                   | Instruction name                                                                                                              | ARM                | MIPS         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------|

|                   | Add                                                                                                                           | add                | addu, addiu  |

|                   | Add (trap if overflow)                                                                                                        | adds; swivs        | add          |

|                   | Add add Add (trap if overflow) adds; swivs Subtract sub Subtract (trap if overflow) subs; swivs Multiply mul Divide — And and | subu               |              |

|                   | Subtract (trap if overflow)                                                                                                   | subs; swivs        | sub          |

|                   | Multiply                                                                                                                      | mul                | mult, multu  |

|                   | Divide                                                                                                                        | -                  | div, divu    |

|                   | And                                                                                                                           | and                | and          |

| Register-register | Or                                                                                                                            | orr                | or           |

|                   | Xor                                                                                                                           | eor                | xor          |

|                   | Load high part register                                                                                                       | -                  | lui          |

|                   | Shift left logical                                                                                                            | Isl <sup>1</sup>   | sllv, sll    |

|                   | Shift right logical                                                                                                           | Isr <sup>1</sup>   | srlv, srl    |

|                   | Shift right arithmetic                                                                                                        | asr <sup>1</sup>   | srav, sra    |

|                   | Compare                                                                                                                       | cmp, cmn, tst, teq | slt/i,slt/iu |

|                   | Load byte signed                                                                                                              | Idrsb              | lb           |

|                   | Load byte unsigned                                                                                                            | ldrb               | Ibu          |

|                   | Load halfword signed                                                                                                          | Idrsh              | lh           |

|                   | Load halfword unsigned                                                                                                        | ldrh               | Ihu          |

|                   | Load word                                                                                                                     | ldr                | lw           |

| Data transfer     | Store byte                                                                                                                    | strb               | sb           |

|                   | Store halfword                                                                                                                | strh               | sh           |

|                   | Store word                                                                                                                    | str                | sw           |

|                   | Read, write special registers                                                                                                 | mrs, msr           | move         |

|                   | Atomic Exchange                                                                                                               | swp, swpb          | II;sc        |

COMP122

Hennessy & Patterson

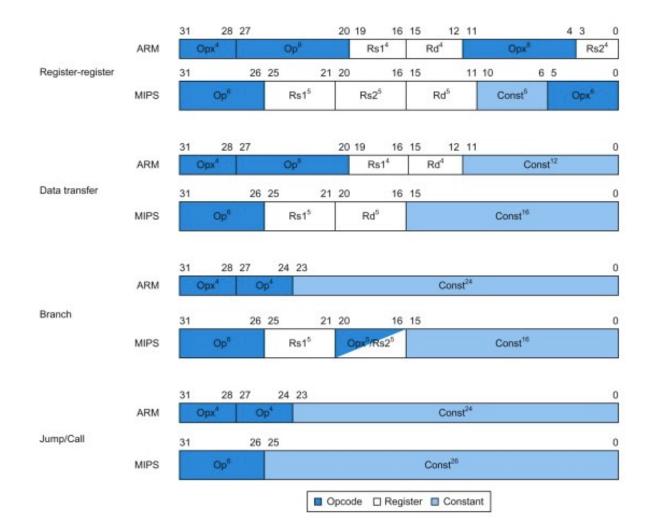

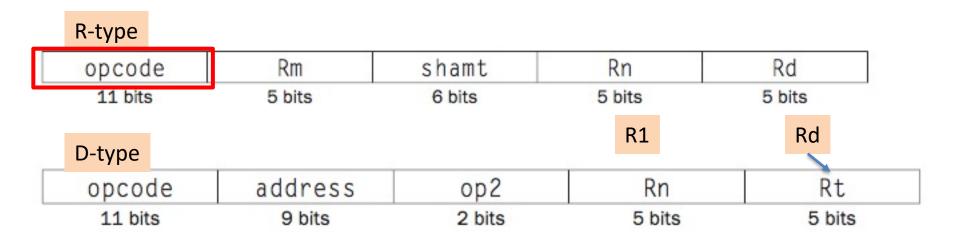

Figure 2.16.4: Instruction formats, ARM and MIPS (COD Figure 2.34).

The differences result from whether the architecture has 16 or 32 registers.

## ARMv8

COMP122

Hennessy & Patterson

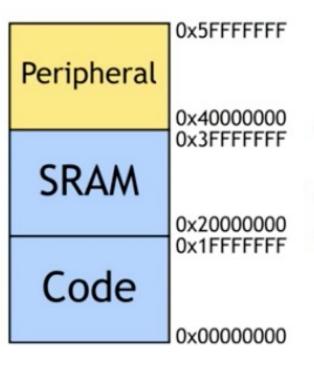

## 2.18 Real stuff: The rest of the ARMv8 instruction set

Of the many potential problems in an instruction set, the one that is almost impossible to overcome is having too small a memory address. While the x86 was successfully extended first to 32-bit addresses and then later to 64-bit addresses, many of its brethren were left behind. For example, the 16-bit address MOStek 6502 powered the Apple II, but even given this headstart with the first commercially successful personal computer, its lack of address bits condemned it to the dustbin of history.

ARM architects could see the writing on the wall of their 32-bit address computer, and began design of the 64-bit address version of ARM in 2007. It was finally revealed in 2013. Rather than some minor cosmetic changes to make all the registers 64 bits wide, which is basically what happened to the x86, ARM did a complete overhaul. The good news is that if you know MIPS it will be very easy to pick up ARMv8, as the 64-bit version is called.

First, as compared to MIPS, ARM dropped virtually all of the unusual features of v7:

- There is no conditional execution field, as there was in nearly every instruction in v7.

- The immediate field is simply a 12 bit constant, rather than essentially an input to a function that produces a constant as in v7.

- ARM dropped Load Multiple and Store Multiple instructions.

- The PC is no longer one of the registers, which resulted in unexpected branches if you wrote to it.

#### Second, ARM added missing features that are useful in MIPS:

- V8 has 32 general-purpose registers, which compiler writers surely love. Like MIPS, one register is hardwired to 0, although in load and store instructions it instead refers to the stack pointer.

- Its addressing modes work for all word sizes in ARMv8, which was not the case in ARMv7.

- It includes a divide instruction, which was omitted from ARMv7.

- It adds the equivalent of MIPS branch if equal and branch if not equal.

## **ARM**

ARMv**7**

#### Cortex-M ISA

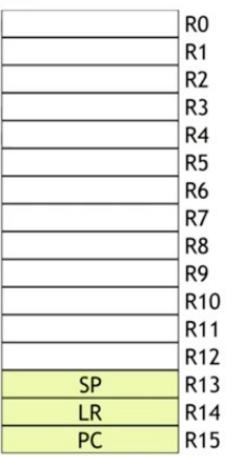

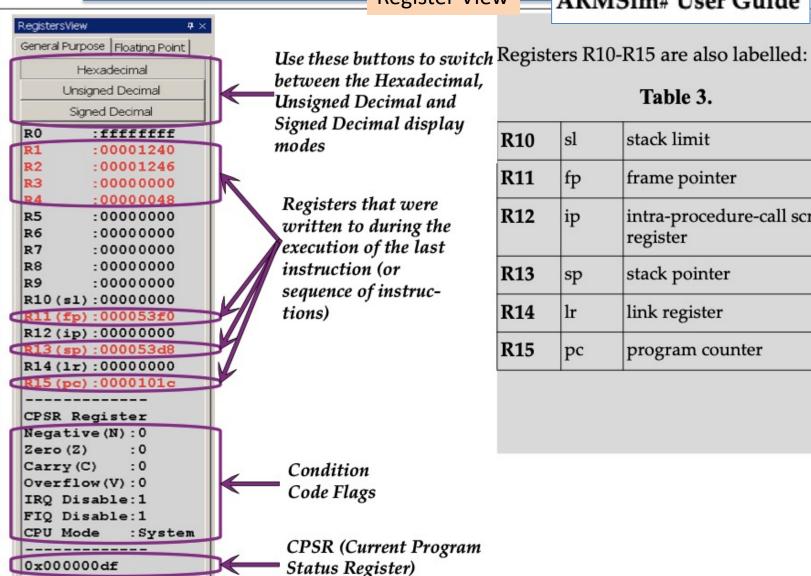

#### Registers

#### Sixteen generic 32-bit registers

- Thirteen are for general purposes

- Can hold data or address

- Data may be byte, halfword, or word

- Three have a special purpose

- R13 is the stack pointer

- R14 is the link register

- R15 is the program counter

## Registers

Hennessy & Patterson

ARMv8

| Name Register<br>number     |                                                                                     | laine – Heape                                                                          |      |

|-----------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------|

| X0-X7                       | 0–7                                                                                 | Arguments/Results                                                                      | no   |

| Х8                          | 8                                                                                   | Indirect result location register                                                      | no   |

| X9-X15                      | 9–15                                                                                | Temporaries                                                                            | no   |