#### Classroom

Rev 7-19-23

## **Tech History**

Part 2

Chips (IC's & MPU's)

by Dr Jeff Drobman

Dr Jeff Software

#### Index

#### Part 2: Chips

- History of Silicon Valley & Chips

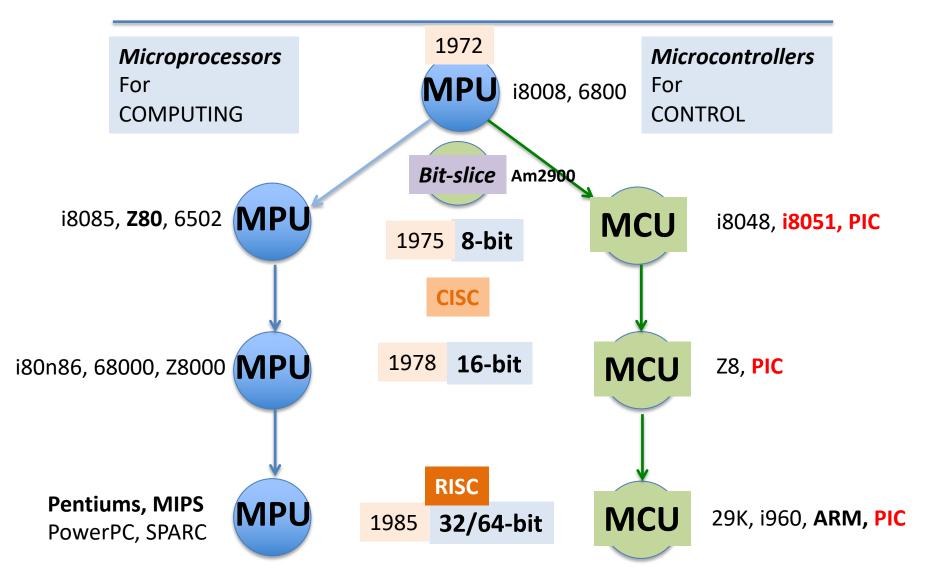

- Microprocessors (MPU/MCU)

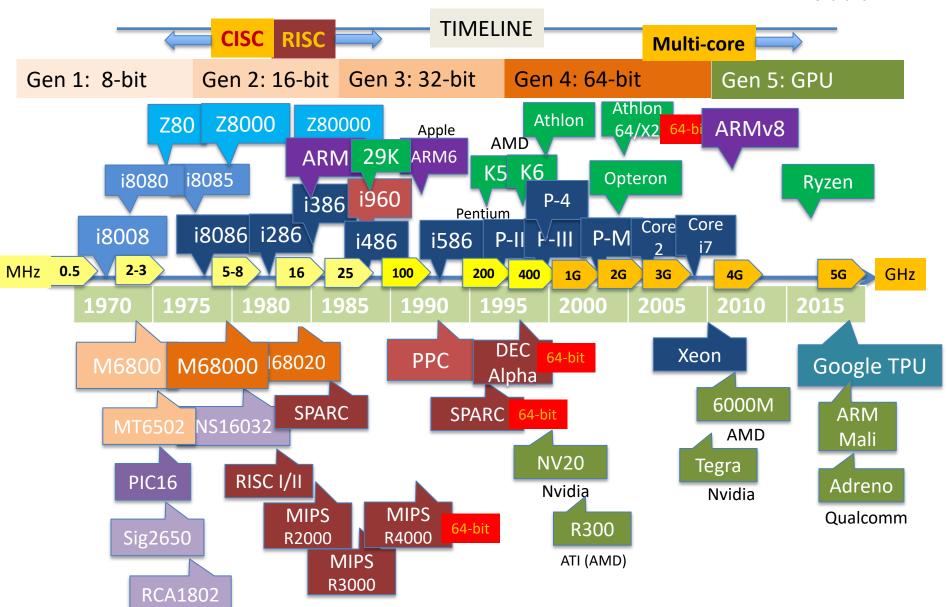

- ☐ Microprocessor Timeline (Exhaustive)

- **Early RISC MPU's**

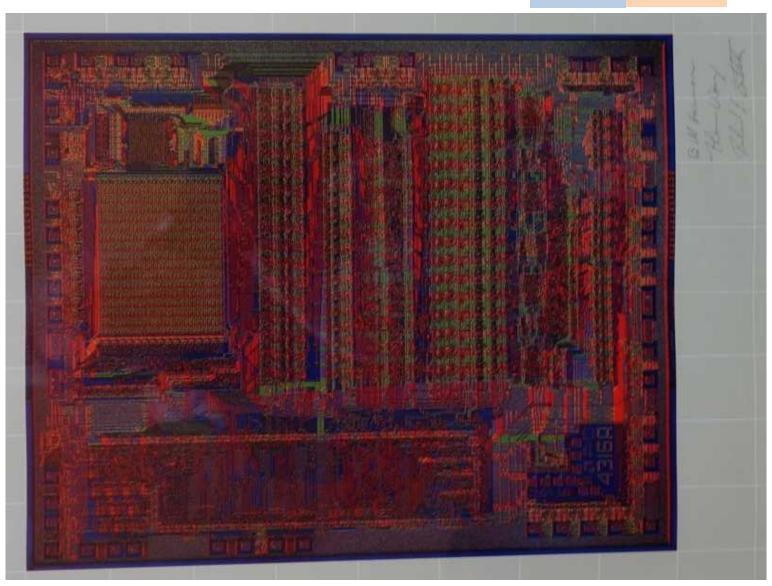

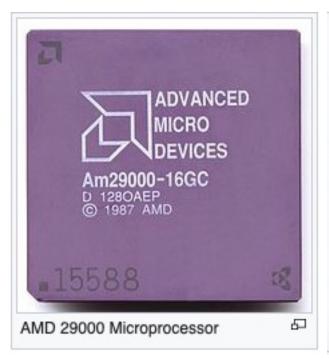

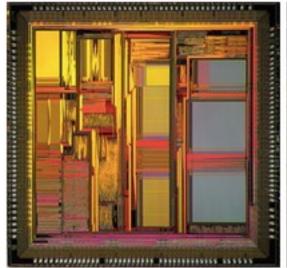

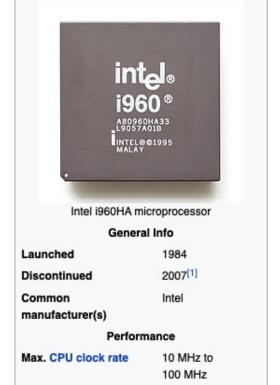

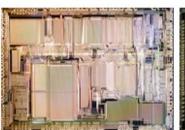

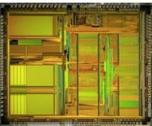

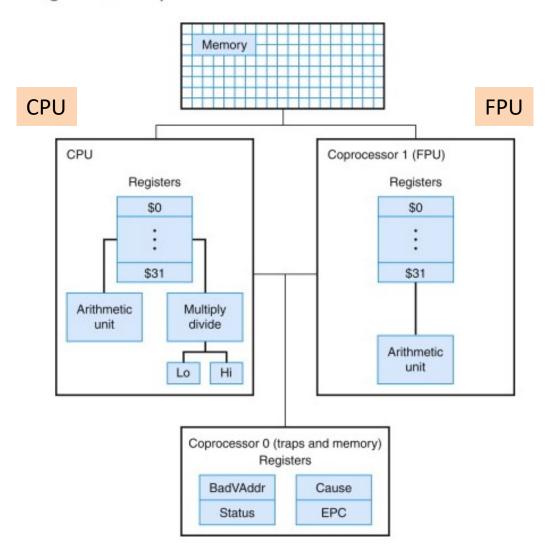

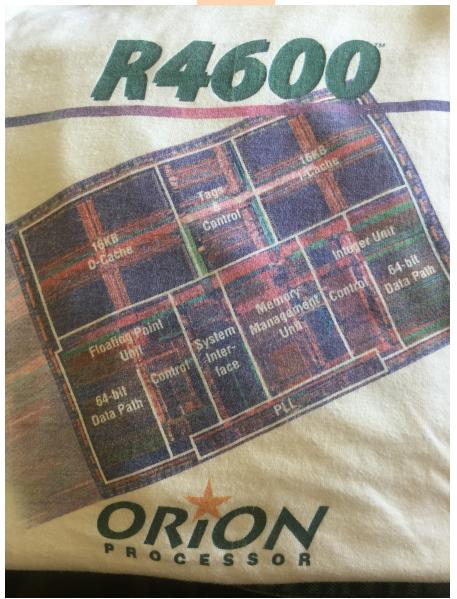

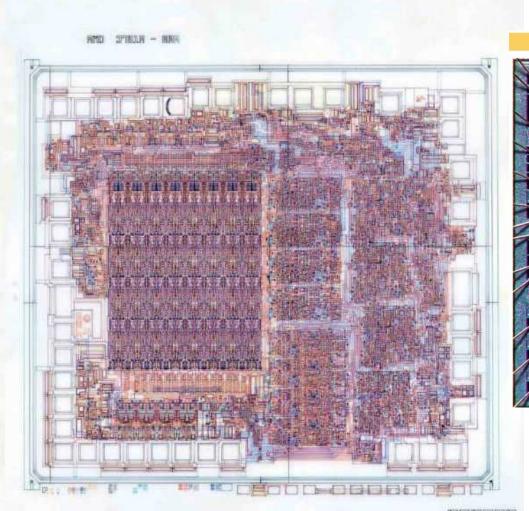

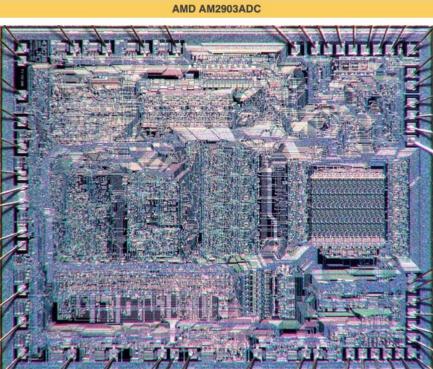

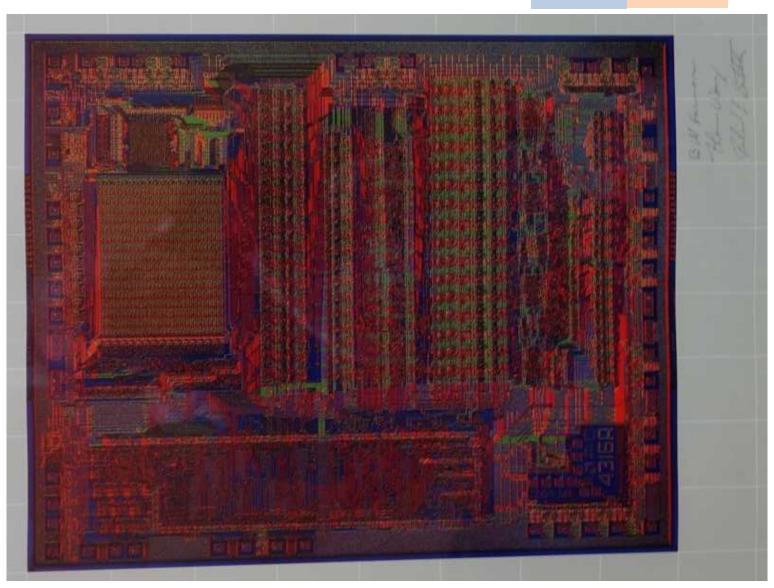

- ☐ AMD 29K, Intel i960, MIPS R2/3/4000

- Advanced RISC MPU's

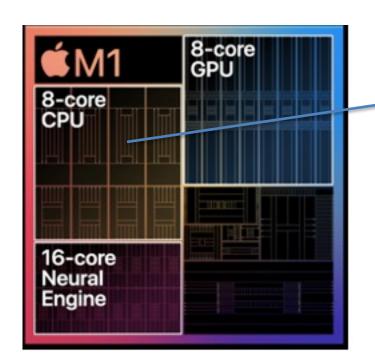

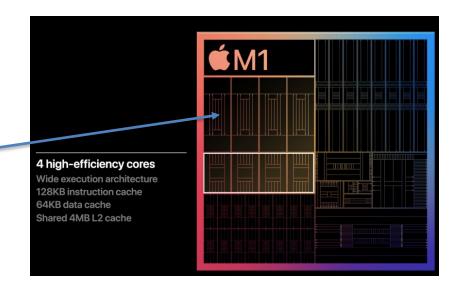

- ☐ Apple, Intel Core, AMD Zen, Mobile SoC

- Chips & Wafer Fabs (see separate file)

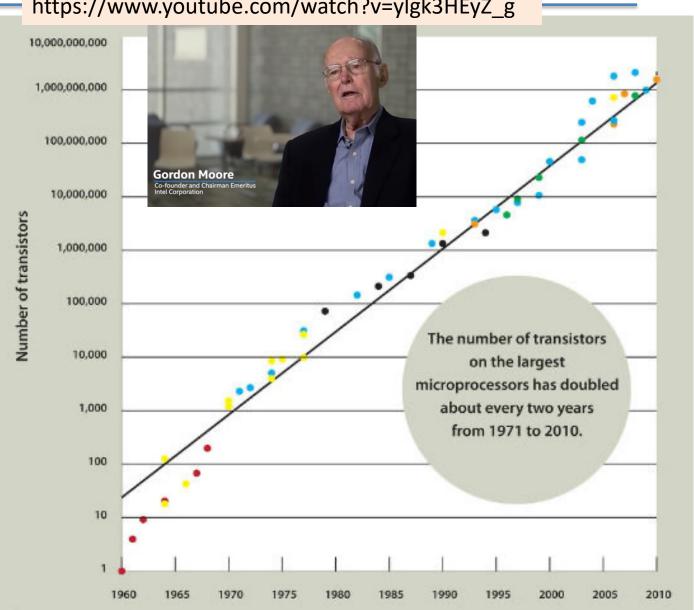

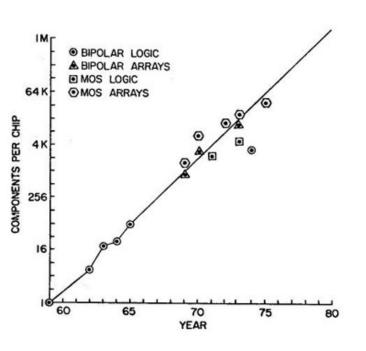

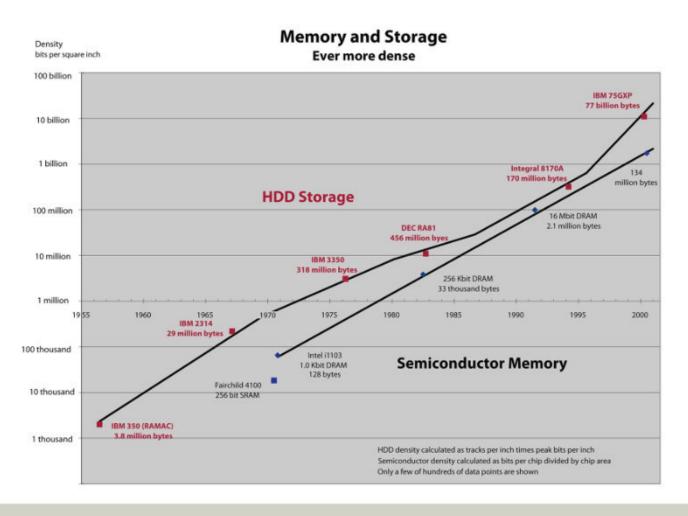

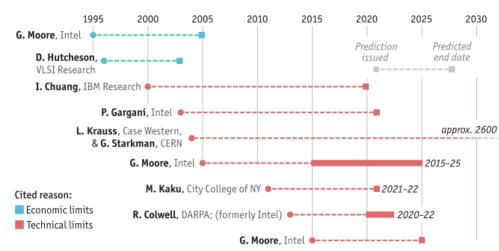

- Moore's Law

- Memories

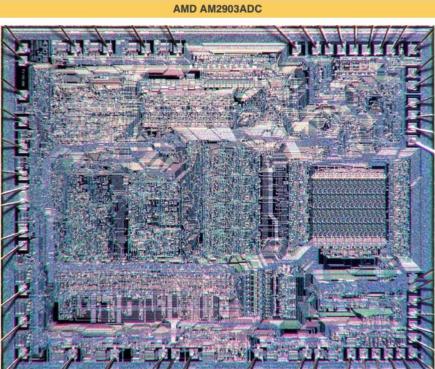

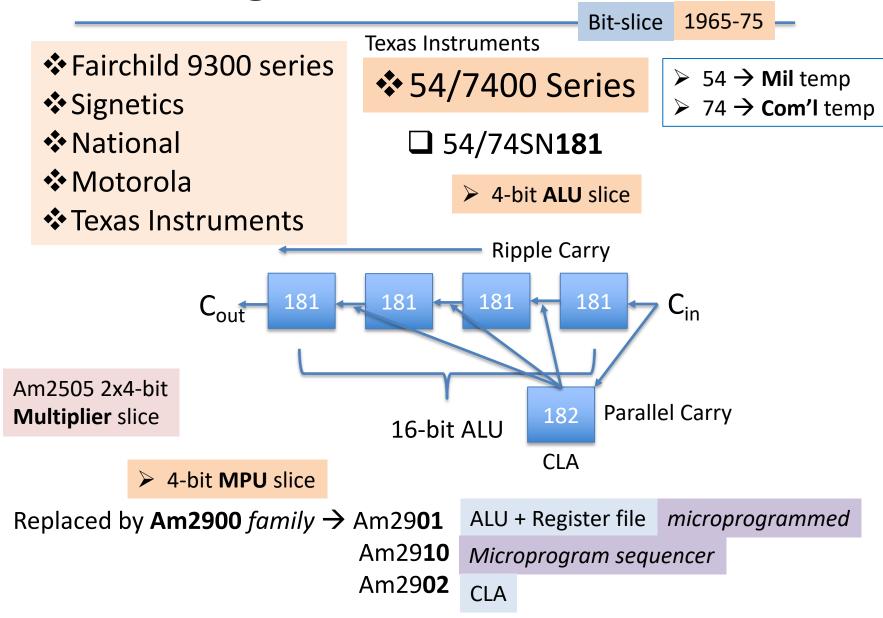

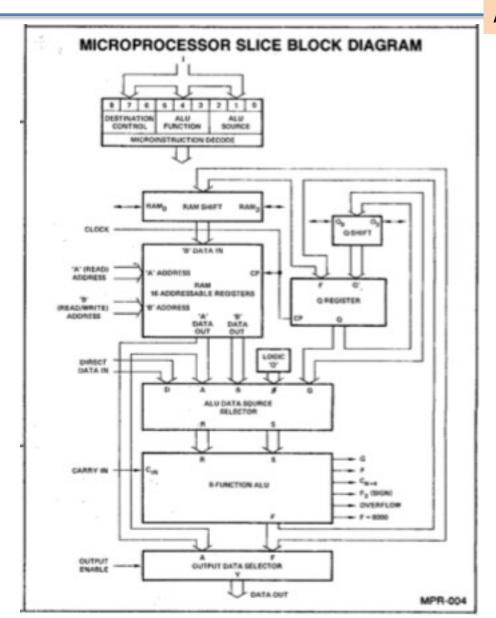

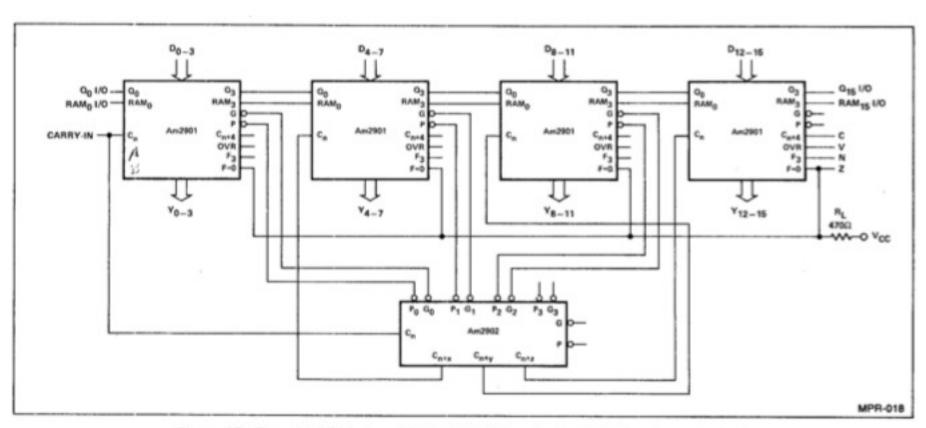

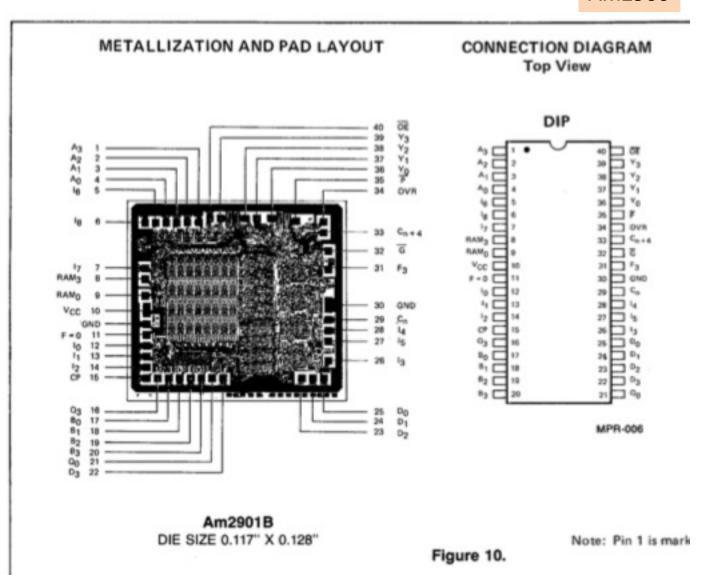

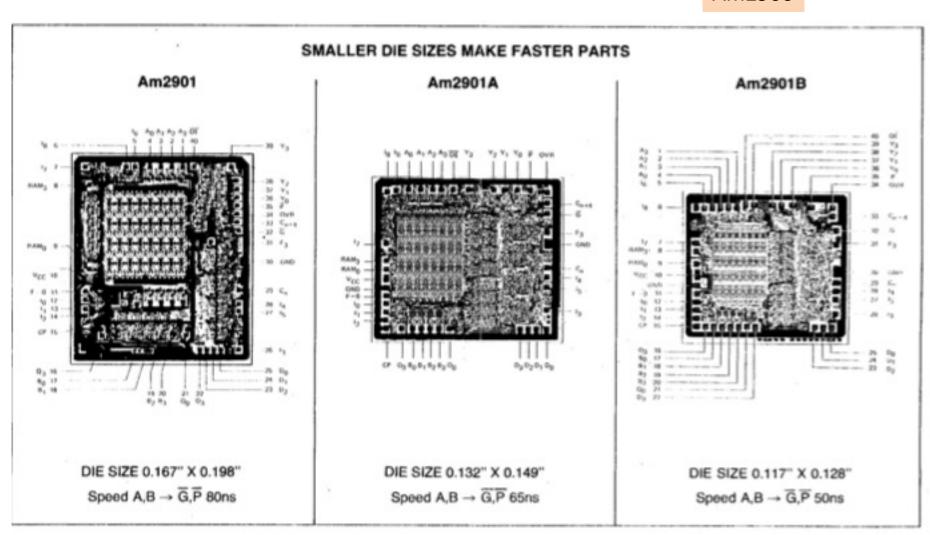

- ❖ Logic (& Bit-Slice MPU)

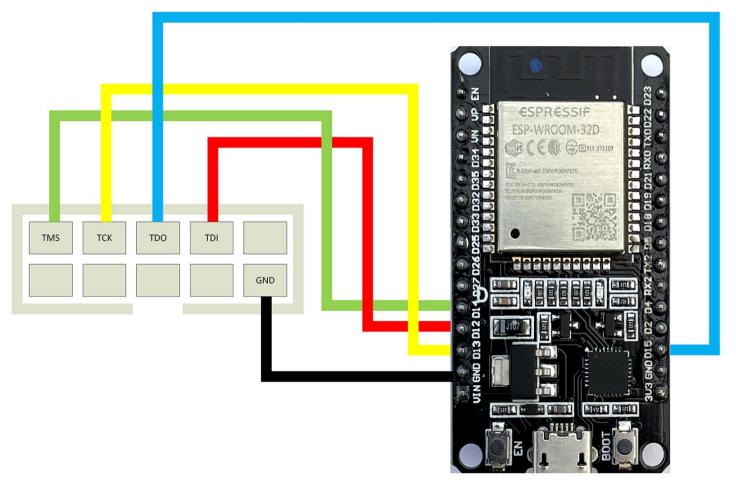

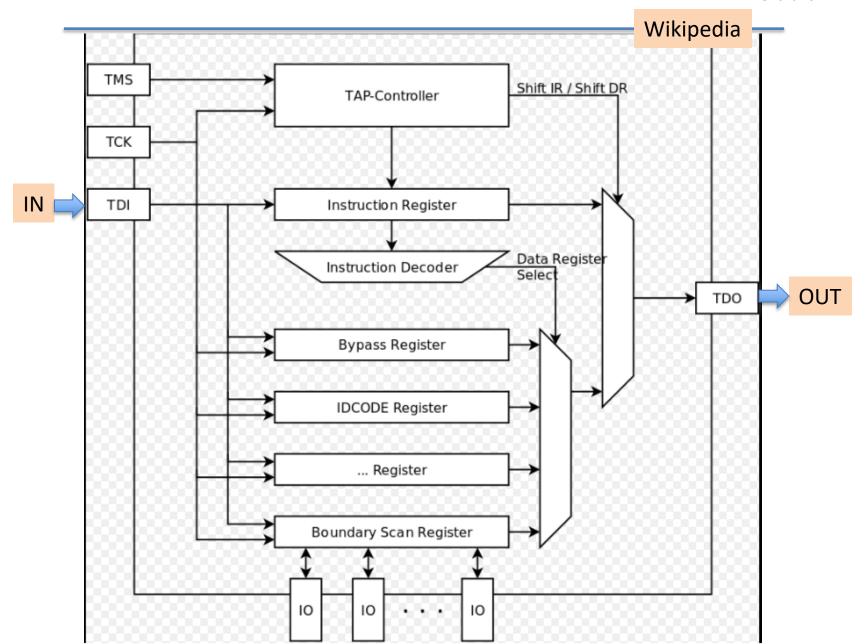

- Debug/Test, JTAG

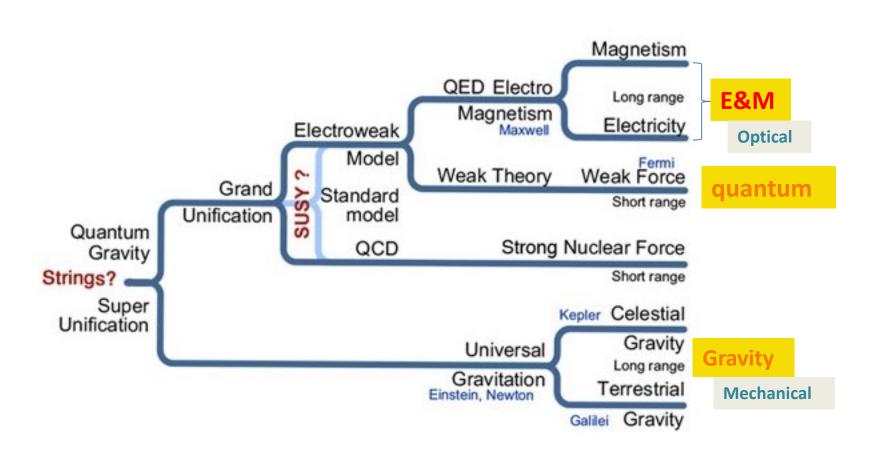

### Physics of Computers

4 Forces in Nature

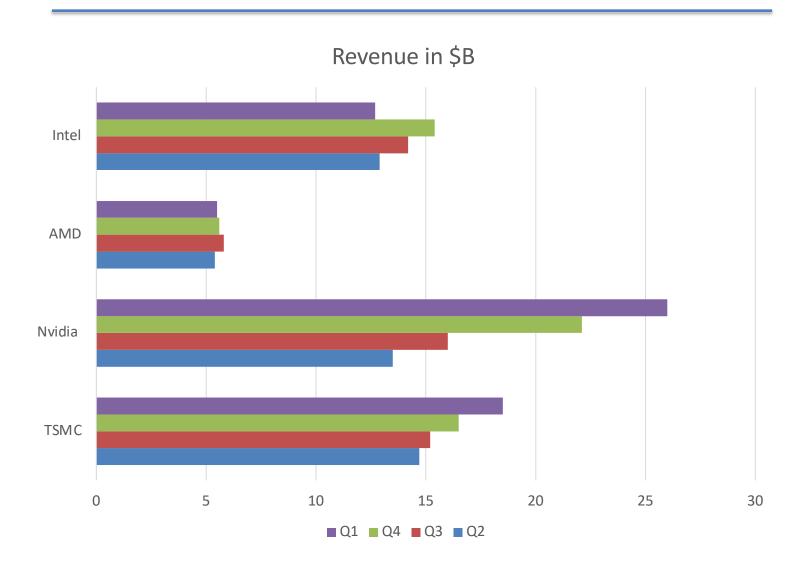

## Chips 2Q23-1Q24

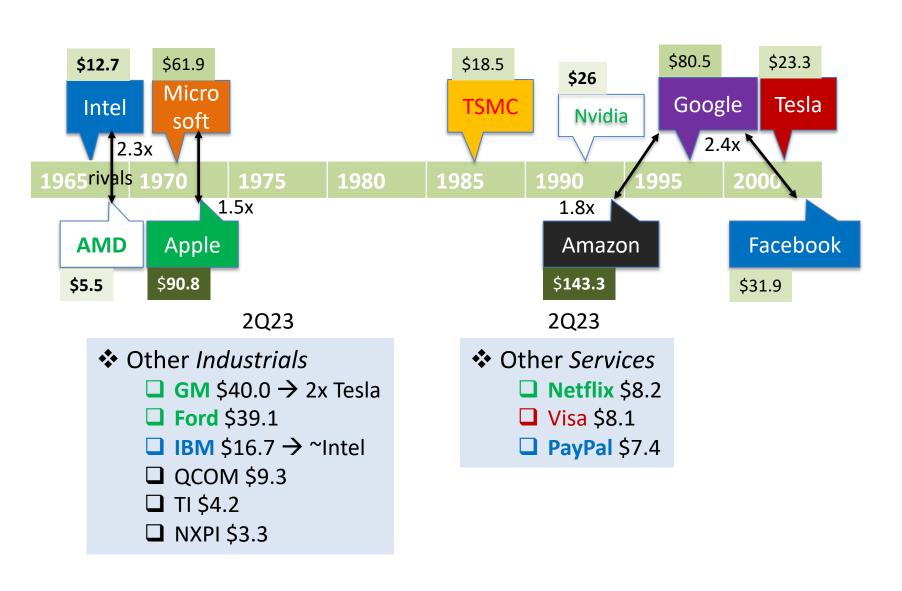

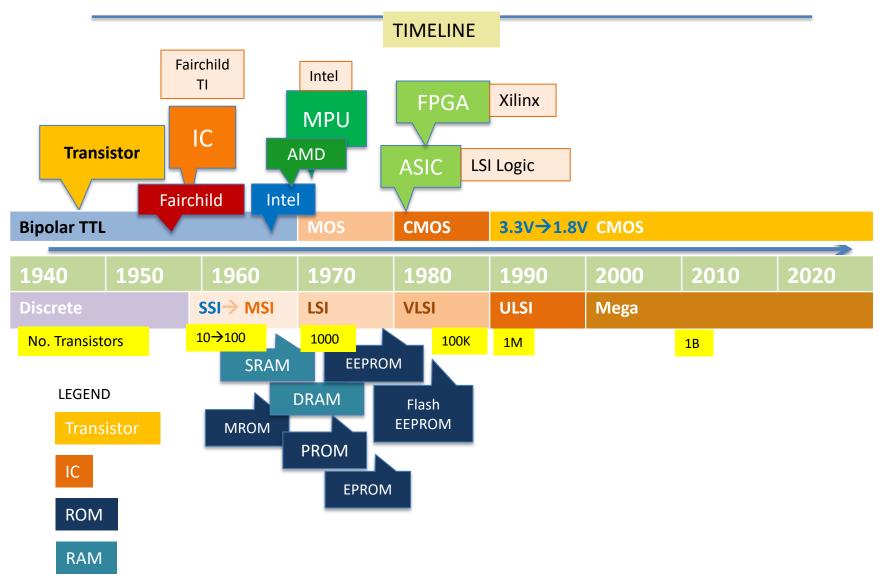

#### **Tech Titan Timeline**

## Chips

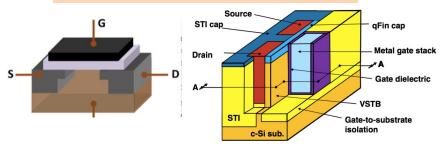

## Transistors

#### The Transistor

size =  $^1$  inch

#### **1947** ushered in the era of *Microelectronics*

A transistor is a semiconductor device used to amplify or switch electronic signals and electrical power. It is composed of semiconductor material usually with at least three terminals for connection to an external circuit. A voltage or current applied to one pair of the transistor's terminal

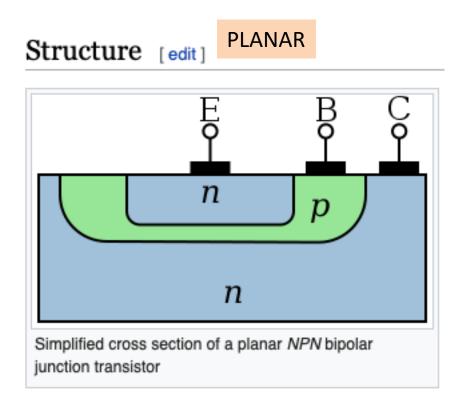

❖ 1947- Bipolar point/junction

❖ 1959- Planar bipolar [10]\*

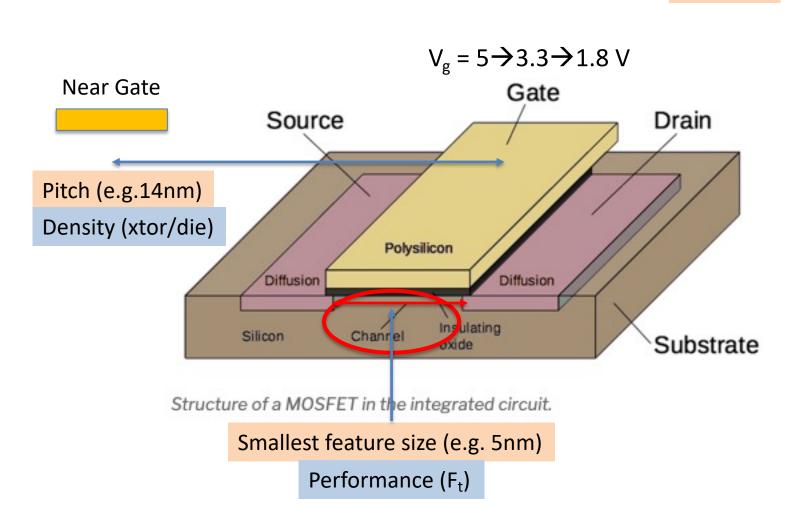

❖ 1964- MOS (P-channel) [100]

❖ 1972- MOS (N-channel) [1,000]

**❖** 1978- CMOS [4,000]

❖ 1990- sub-micron [10,000]

**2000- 100 nm** [100,000]

**❖** 2011- FinFET [1,000,000]

\*no. of transistors

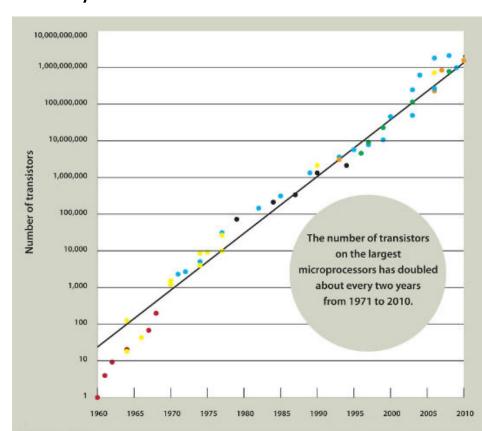

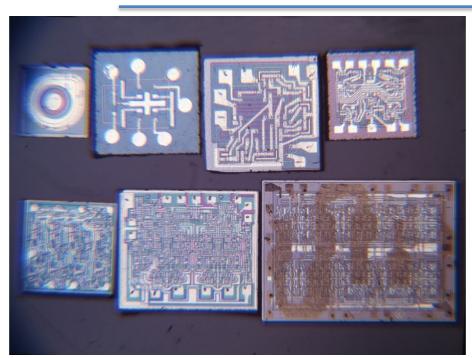

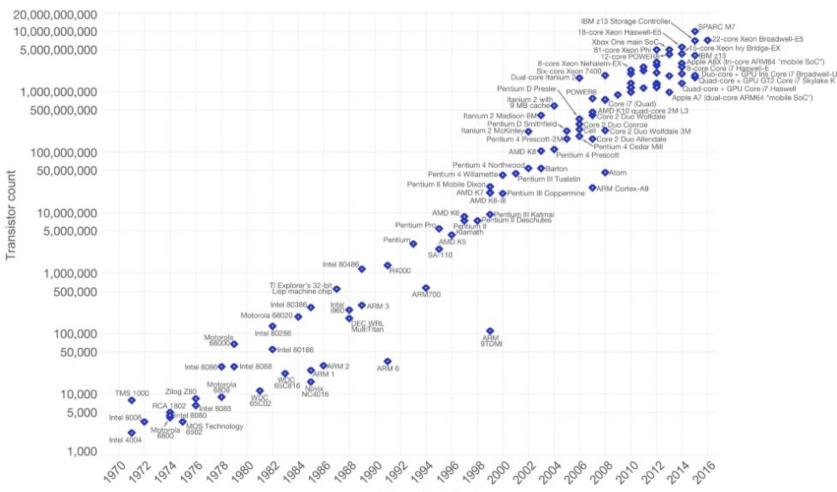

Transistors have been shrunk every 2 years according to *Moore's Law*

\* size = 10 nm =  $4x10^{-7}$  inches

❖ yields → ~1M devices per cm²

### **Viewing Transistors**

Quora

How are billions of transistors compressed into a single chip? Can a transistor in the chip be seen with a microscope?

**Jeff Drobman**Works at Dr Jeff Software ⋅ Just now ⋅ ⑤

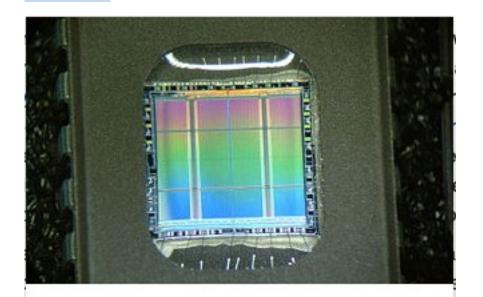

once a chip is complete, only the top few layers of metal interconnect are visible (unless etched away). a single transistor is way too small to be readily identified, as they are now as small as about 25–40 nm in overall size. note that a "5nm" node means that only the channel length is that small. the overall transistor size, and pitch, is more like 25–40 nm.

#### **Transistor Atoms**

Al Kordesch, Semiconductor Device Modeling

Answered Feb 1, 2019

How many atoms are in a typical transistor in a chip?

Short Answer: 49,000 atoms!

**Apple's iPhone XS uses 7 nanometer transistors.** So let's estimate how many atoms are in one of them. Excluding the connecting wires and other parts, I'm just going to calculate the size of the active part, the "channel" under the gate. The volume of the channel is about  $(7 \text{ nm long}) \times (7 \text{ nm deep}) \times (20 \text{ nm wide})$ . The atomic density of silicon is 5E+28 atoms per cubic meter. So let's go!

Number of atoms n = volume x density

$n = (980E-27) \times (5E+28) = 49,000$ atoms.

Silicon atomic radius = .111nm  $\rightarrow$  **4.5** atoms/nm

Cubic:  $4.5^3 = 91$  atoms/cu nm

Channel volume @5n: 5x5x18 = 450 cu nm

Cubic: 91\*450 = **40,950** atoms/channel

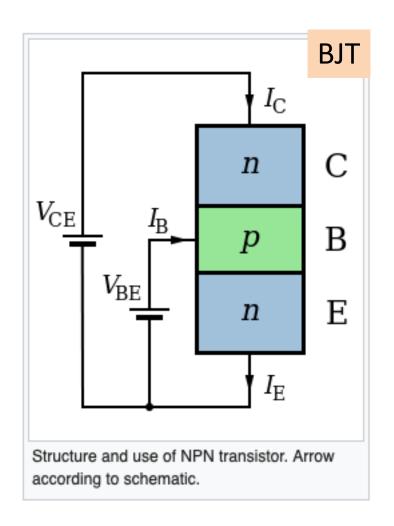

## **Bipolar Transistors**

## Bipolar/MOSFET Transistors Jeff Drobmar © 2016-23

SOFTWARE

NOTE APP DEVELOPER

SPECIAL DEVELOPMENT

**Schematics** Differences Between BJT & FET Transistors Collector Drain Gate Base Slower Faster ❖ Smaller Larger More power Less power BJT

Current flows opposite electrons (C->E, S->D)

(N-Channel FET/JFET)

❖ B, G are inputs (H/L)

(NPN Transistor)

- ❖ B, G voltages turn transistor ON/OFF

- Outputs (not shown) are tied to C, D

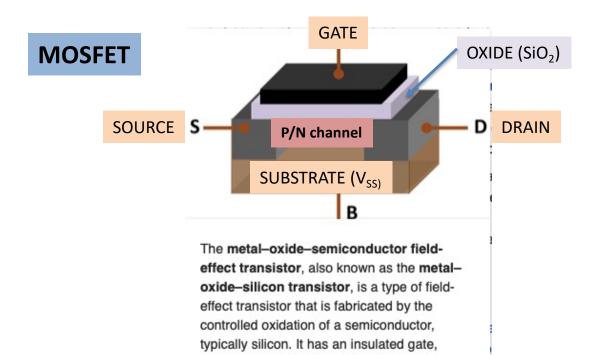

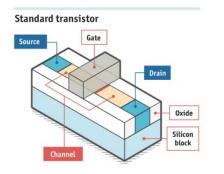

#### **MOS Transistor**

WikiSemi

## Chips

## Chip History

### Levels of Integration

#### IC Process & Interface

TTL compatible − 5V → 3V

#### Bipolar

**5V**

ightharpoonup RTL

ightharpoonup DTL

ightharpoonup TTL

ightharpoonup Schottky TTL

ightharpoonup LS TTL

1960 1965 1970 1975 1980 1985 1990 **♣** MOS **BiCMOS**

$\rightarrow$  PMOS $\rightarrow$ NMOS $\rightarrow$  CMOS $\rightarrow$  CMOS $(\overline{TTL} I/O)\rightarrow$  3.3V

$5V \rightarrow 3V$

whose voltage determines the conductiv

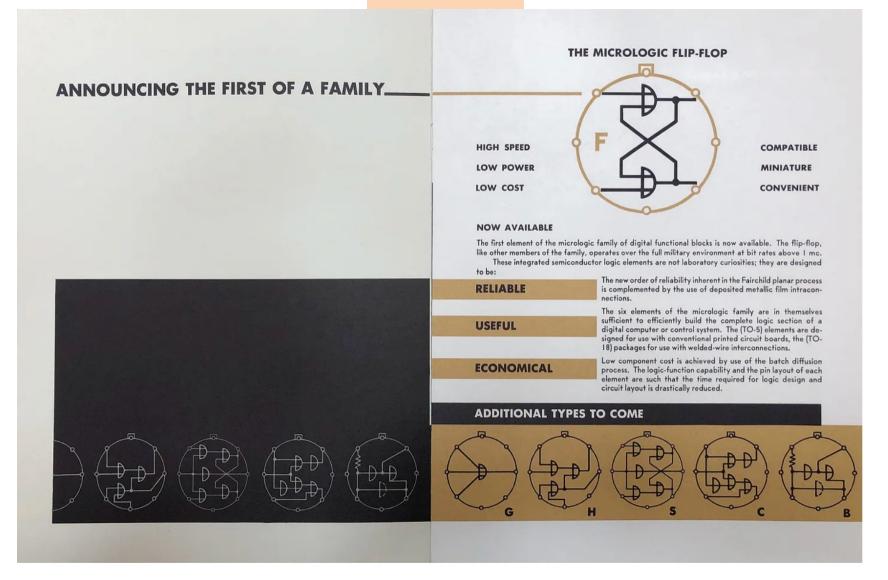

## 1st Flip-Flop Chips

Fairchild 1961

## 1st Flip-Flop Chips

Fairchild 1961

#### Old Computer Tech

Discretes R/T

This is a circuit board from an IBM 7040, built in 1963.

**Discrete** Transistors

There are no small components there. Those horizontal cylinders are maybe half an inch (12mm) long.

### Old Computer Tech

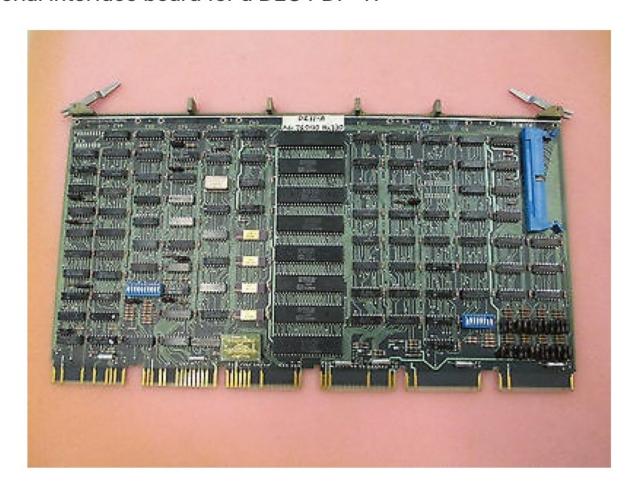

MSI/LSI IC's

This is a serial interface board for a DEC PDP-11

The integrated circuits were very simple with only a few dozen transistors in, so they didn't need very precise machines to make them. The boards could still be assembled by hand.

## Old Computer Tech

LSI IC's

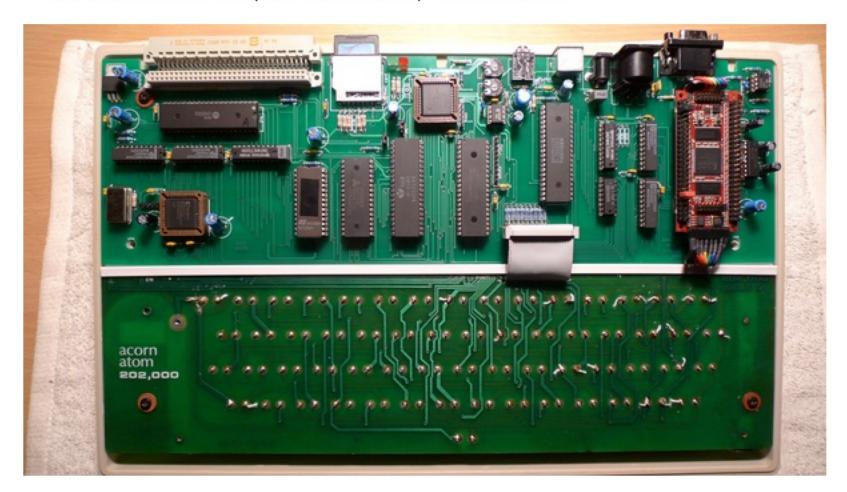

This is the second computer I assembled, the Acorn Atom

### **New Computer Tech**

VLSI IC's

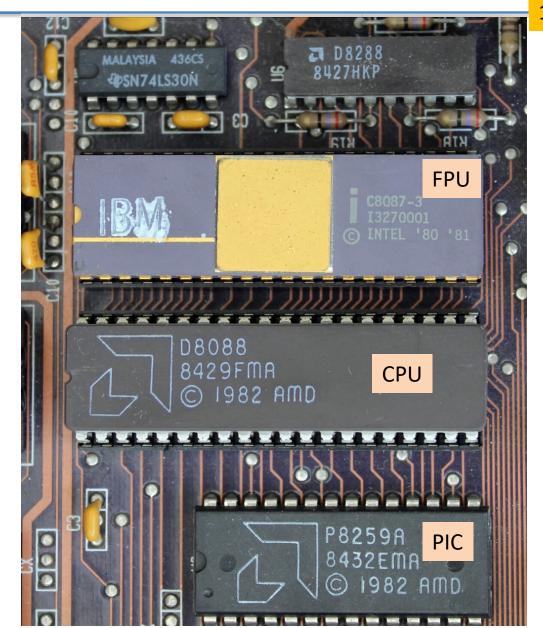

### IBM PC Chips

1981

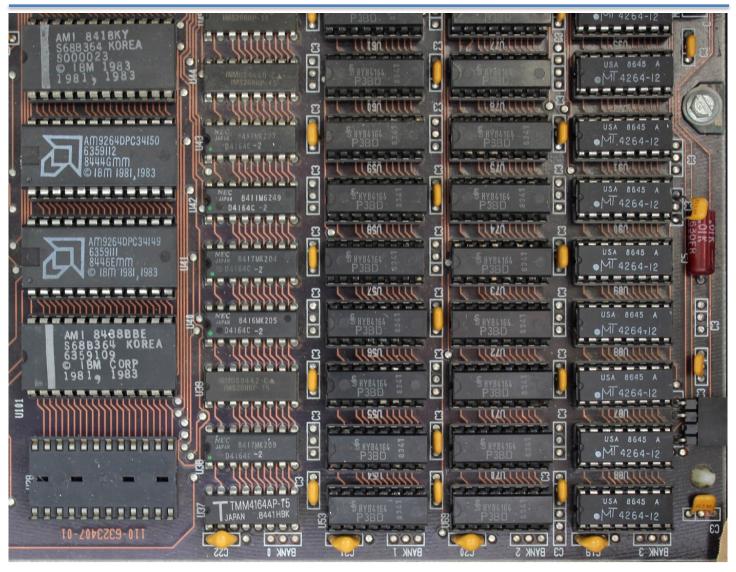

# IBM PC – Large Motherboard Frobbinan

The memory is organised in four banks in the bottom right corner of the motherboard – in this case there are four 64KB banks, adding up to a total of 256KB

# Early Semiconductors & IC's Jeff Drobman © 2016-23

#### **MILESTONES**

| trans   | 1947   |    | *        | <u>Transistor</u> invented (Bell Labs' Bardeen, Brattain, <b>Shockley</b> ) - point contact form                  |

|---------|--------|----|----------|-------------------------------------------------------------------------------------------------------------------|

|         | 1951   |    | **       | Bipolar junction transistor (BJT) invented by Wm Shockley                                                         |

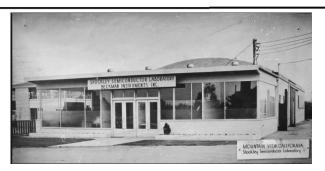

|         | 1956   |    | **       | Shockley Semiconductor Laboratory founded as a division of Beckman Instruments                                    |

|         |        |    |          | Shockley hires his PhD students Robert Noyce, Gordon Moore, et al.                                                |

| Fairchi | ld 195 | 57 | **       | "Traitorous 8" leave Shockley Labs, found Fairchild Semiconductor                                                 |

|         | Mar    |    | <b>*</b> | TI— Jack Kilby tests the world's first integrated circuit (Sgl-transistor oscillator on germanium)                |

|         | 1959   |    | <b>*</b> | Jean Hoerni of Fairchild demos his "planar process" (world first)                                                 |

| IC      |        |    |          | Bob Noyce documents a method for building ICs using that planar process                                           |

| May     | 1960   |    | *        | Fairchild group makes first <u>IC</u>                                                                             |

|         |        |    |          | > [Courts and the tech community decided to give equal rights to the invention of the IC to both Kilby and Noyce] |

|         |        |    | **       | MOS (linear) invented: first MOSFET amplifier demonstrated                                                        |

| MOS     | 1963   |    | **       | standard <u>logic</u> families are introduced using DTL and TTL structures                                        |

|         |        |    | **       | CMOS process was invented by Fairchild Semiconductor in a 1963 paper and patent                                   |

|         | 1964   |    | *        | MOS (digital)— 1st products released by General Microelectronics for a calculator chipset                         |

|         |        |    | **       | Linear IC's – 1st analog ICs introduced by Fairchild Semiconductor                                                |

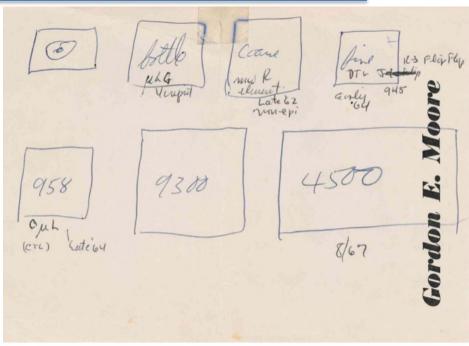

| Apr     | 1965   |    | **       | Moore's Law born - Gordon Moore publishes his first version                                                       |

|         |        |    | <b>*</b> | CMOS– 1 <sup>st</sup> parts by RCA                                                                                |

|         |        |    | <b>*</b> | <b>ROM</b> – 1 <sup>st</sup> Semiconductor                                                                        |

|         |        |    | **       | DIP packages                                                                                                      |

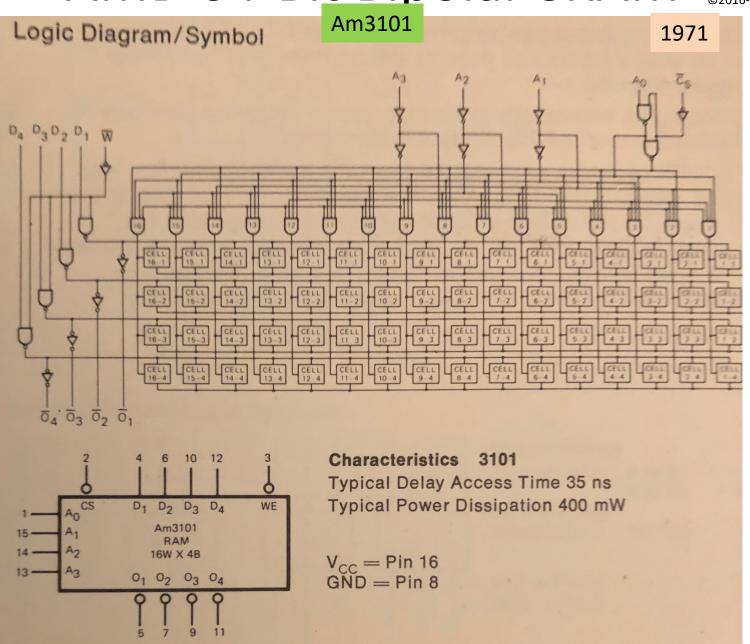

|         | 1966   |    | **       | RAM Bipolar RAMs (SRAM) introduced                                                                                |

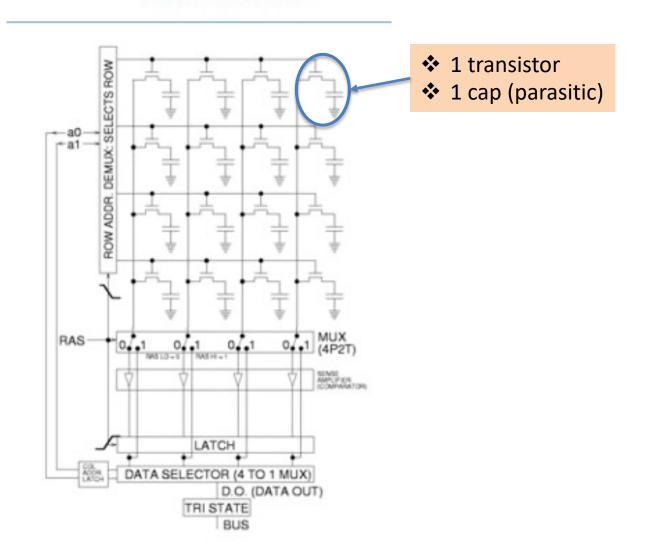

| RAM     |        |    | <b>*</b> | DRAM- IBM conceives DRAM cell (1T, 1C)                                                                            |

|         | 1968   |    | *        | CMOS SRAM- 1 <sup>st</sup> parts by RCA                                                                           |

1968-2011

#### Semiconductors & IC's

|       | 1968 | ❖ Intel founded                                                                            |

|-------|------|--------------------------------------------------------------------------------------------|

|       |      |                                                                                            |

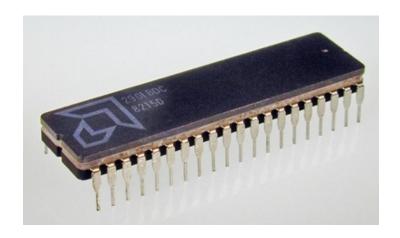

|       | 1969 | AMD founded                                                                                |

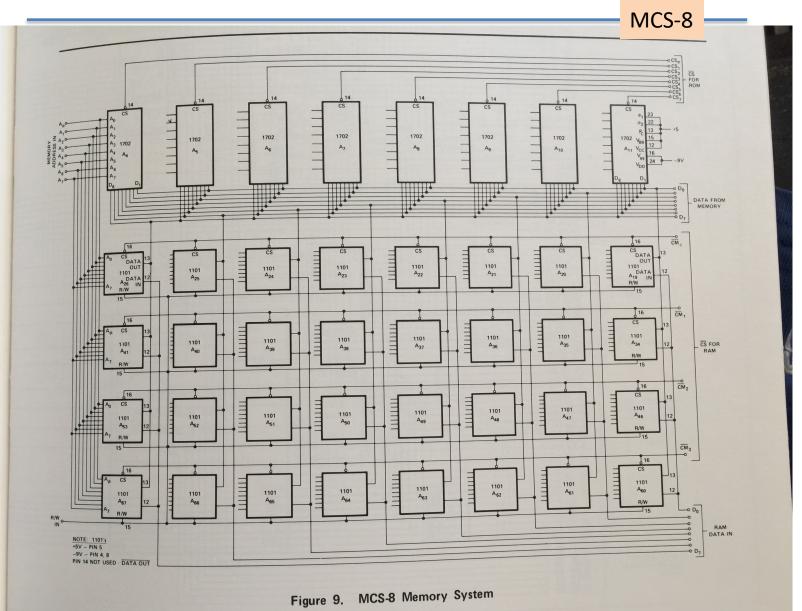

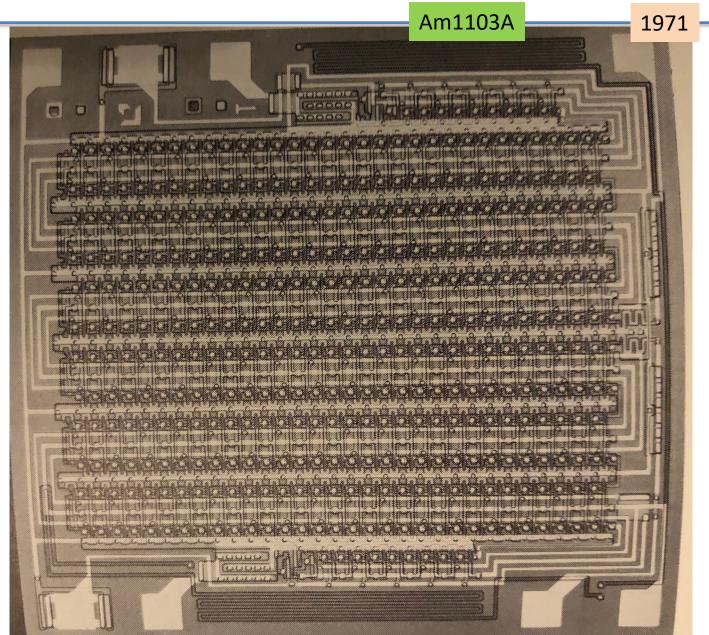

| MPU   | 1971 | Microprocessor & RAM in MOS invented by Intel (i4004/i8008, i1101/3)                       |

|       | 1972 | Ion Implantation (replaces chemical diffusion) Mfg process                                 |

|       | 1974 | ❖ Digital <b>Watch</b> IC invented                                                         |

|       | 1978 | ❖ Wafer stepper invented for fabs Mfg process                                              |

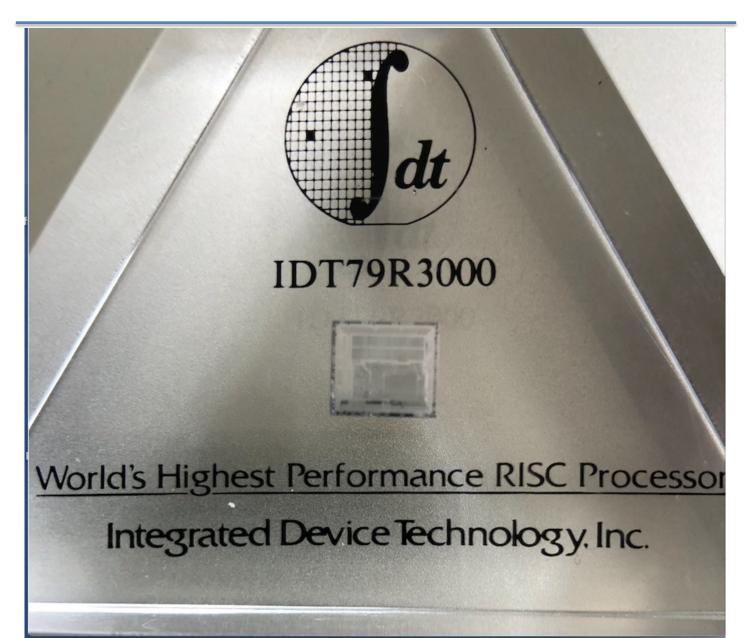

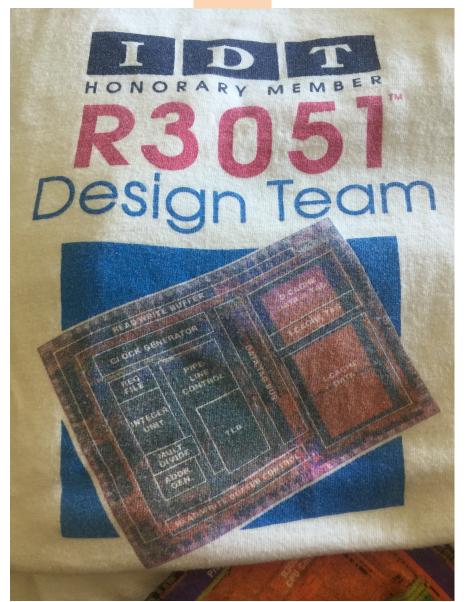

|       | 1979 | IDT founded (CMOS) Mfg process                                                             |

| ASIC  | 1981 | LSI Logic founded (ASIC)                                                                   |

| FPGA  | 1984 | Xilinx makes 1 <sup>st</sup> FPGA, MIPS founded as early RISC pioneer (licenses LSI & IDT) |

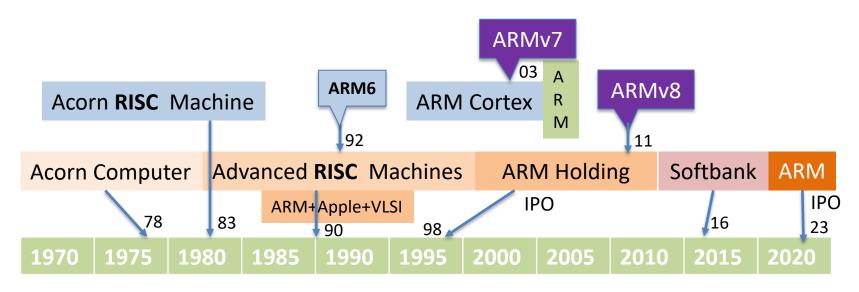

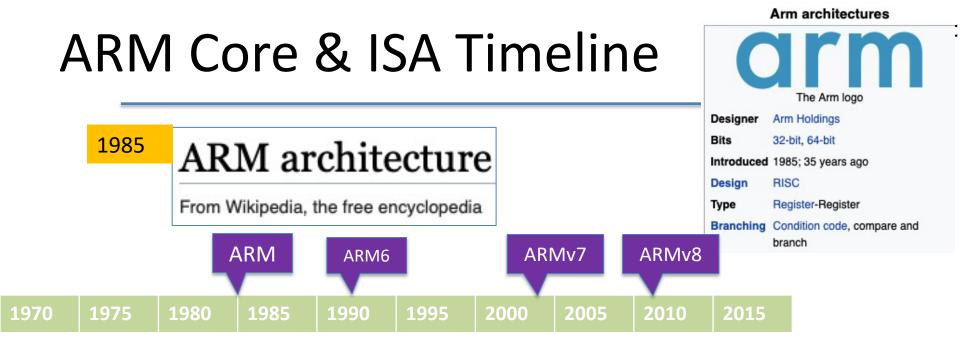

|       | 1985 | ARM founded as Acorn RISC Machines                                                         |

| Flash | 1987 | Toshiba intro's Flash EEPROM, TSMC founded (foundry) Mfg process                           |

| GPU   | 1998 | ❖ Nvidia founded (1993) – 1 <sup>st</sup> GPU's (1998)                                     |

|       | 2002 | Intel goes to 300mm (12in) wafers Mfg process                                              |

|       | 2009 | AMD spins off fabs to <b>Global Foundries</b> (owner Abu Dhabi) Mfg process                |

|       | 2011 | ❖ Intel FinFET Mfg process                                                                 |

| _     |      |                                                                                            |

| Dec   | 2019 | ❖ Intel intro's 1 <sup>st</sup> QC chip ("Horse Ridge")                                    |

|       | 2020 | ❖ ARM intro's "backside power" process Mfg process                                         |

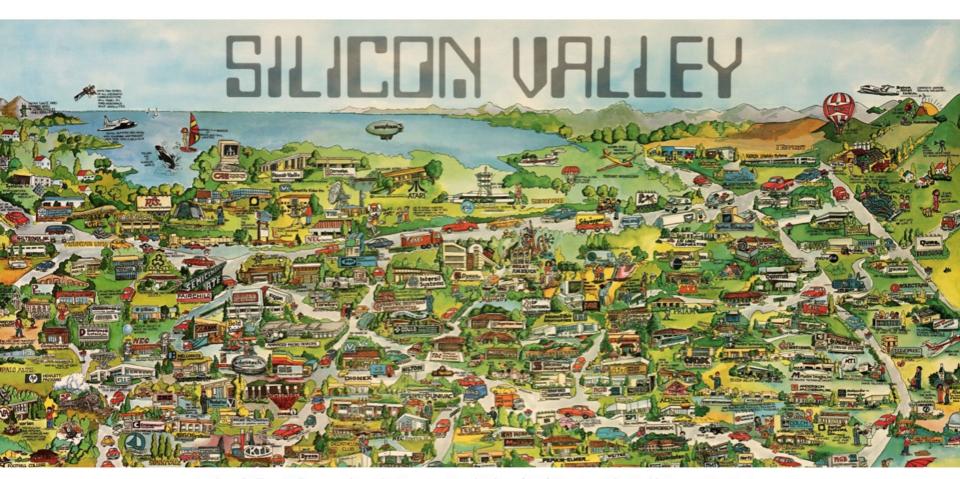

## Silicon Valley

Portion of Silicon Valley map. drawn by Maryanne Regal Hoburg (1982). Courtesy: The David Rumsey Map Center, Stanford University Library

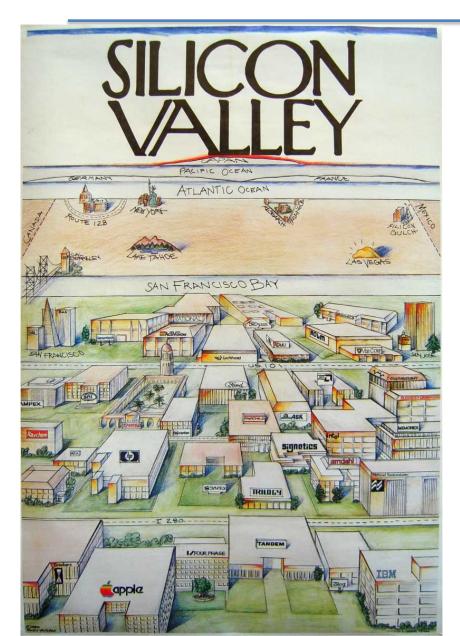

## Silicon Valley

### Founding Fathers

NEW & OLD

#### Missing:

- IC fathers

- Internet fathers

# CHM Computer History Museum CHM on Shockley

https://computerhistory.org/blog/beckman-shockleyand-the-60th-anniversary-of-the-birth-of-silicon-valley

CHM BLOG CURATORIAL INSIGHTS . REMARKABLE PEOPLE

#### BECKMAN, SHOCKLEY AND THE **60TH ANNIVERSARY** OF THE BIRTH OF SILICON VALLEY

By David Laws | February 10, 2016

# M Computer History CHM on Shockley

None would have the same lasting impact on the fortunes of the future Silicon Valley and beyond as Dr. Arnold Beckman's disclosure of an agreement signed the previous day for "the establishment in the Stanford community of the Shockley Semiconductor Laboratory to develop and produce transistors and other semiconductor devices."

#### **ABOUT THE AUTHOR**

David A. Laws [AMD 1975-1986, V.P. Business Development] is a high-technology business consultant with a focus on marketing and strategic planning. He earned a B.Sc. (Physics) in the UK and after moving to California in 1968 worked for Silicon Valley companies, including Fairchild Semiconductor, Advanced Micro Devices (AMD), and Altera Corporation, in roles from product marketing engineer to CEO.

#### My Genesis Article

#### Genesis: A Silicon Valley Tale

**FECH HISTORY ARTICLE**

BY DR JEFF DROBMAN

#### **Highlights**

- Fairchild founding

- Intel founding

- AMD history

- AMD Intel rivalry

- Search for CMOS

- RISC CPU Architecture

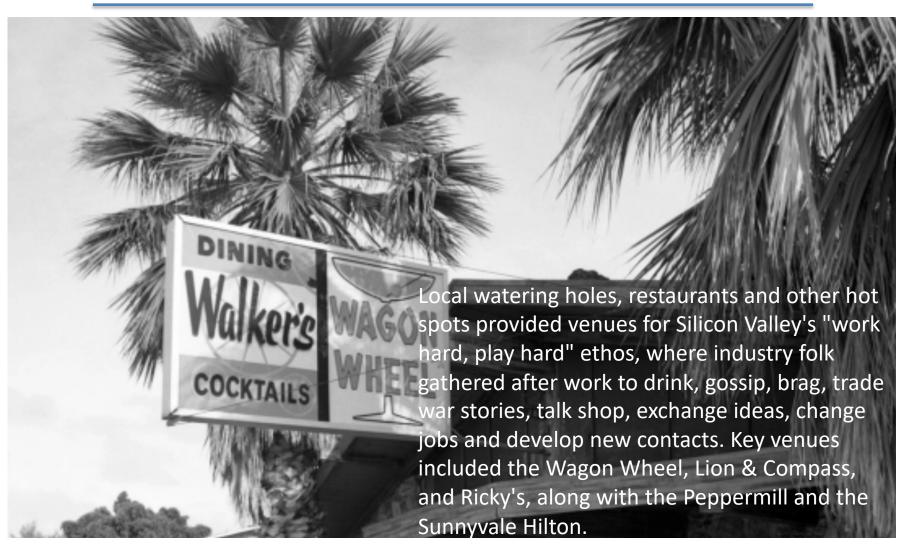

- Legendary Parties & Conferences

- Anecdotes

- Valley Significant Others

- Genesis org-chart

- Process Technology Evolution

- Anniversaries of Technologies

### My Genesis Article

#### The Legend

It has long been legendary that companies in Silicon Valley got started in garages and beach houses, and I am setting the record straight: It is true. Apple was started in Steve Wozniak's garage, when friend Steve Jobs came by and saw his hobby computer. Advanced Micro Devices (AMD) got its start in founding president Jerry Sanders' rented Malibu beach house, on a chilly December evening in 1968 though the house was heated considerably by those entrepreneurial fires. AMD was incorporated 5 months later (May 1969).

#### Genesis of Silicon Valley

https://www.eetimes.com/the-new-silicon-frontier-chapter-4-startup-fever-and-venture-capital/

**DESIGNLINES** | EE LIFE

# The New Silicon Frontier Chapter 4: Startup Fever and Venture Capital

#### MELTING POT FOR THE FAIRCHILDREN

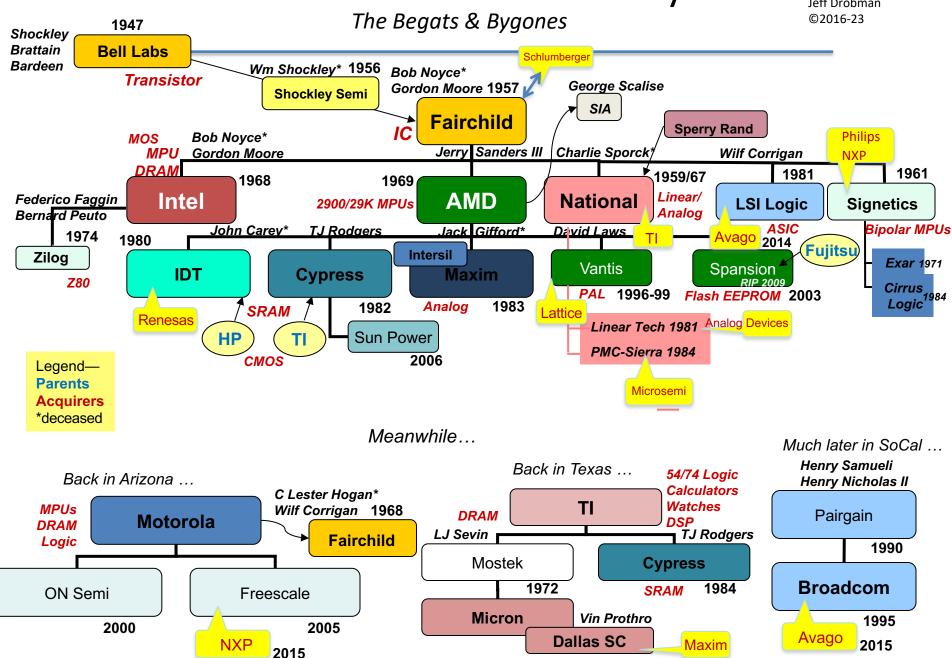

Sheldon Roberts, Eugene Kleiner, and Jean Hoerni's collective decision to leave and compete against Fairchild, just over three years after the company was founded, was the first of what would be many subsequent defections and spinouts, eventually known as "Fairchildren," directly or indirectly creating dozens of corporations, including Intel and AMD. In doing so, Fairchild sowed the seeds of innovation across multiple companies in the region that would eventually become known as Silicon Valley.

While it is unclear who came up with the moniker, "Silicon Valley," Don Hoefler, a technology reporter for the industry publication *Electronic News*, is often credited with popularizing the name in a 1971 column about the region's chip industry. Hoefler also promoted the area's innovative qualities, and was one of the first writers to chronicle the Northern Californian technology industry as a community.

Don Hoefler

#### THE FAIRCHILD LEGACY

Throughout the first half of the 1960s, Fairchild was the undisputed semiconductor leader, forging ahead across all industry segments, be it design, technology, production or sales. Early sales and marketing efforts were modest and military-oriented; that changed in 1961 when Robert Noyce and Tom Bay recruited a group of aggressive salesmen and marketing specialists, including Jerry Sanders III and Floyd Kvamme. The newcomers transformed Fairchild's sales and marketing departments into one of the industry's legends.

Among the pivotal moments was Fairchild's entry into the consumer TV market. Attracted by potential high volumes, Sanders wanted to replace the tube (valve) CRT driver with a transistor, but the target price was U.S. \$1.50. Transistors at that time were selling to the military for \$150.00. In what can only be regarded as a massive leap of faith, Noyce's instructions to Sanders were, "Go take the order, Jerry. We'll figure out how to do it later. Maybe we'll have to build it in Hong Kong and put it in plastic, but right now let's just do it."

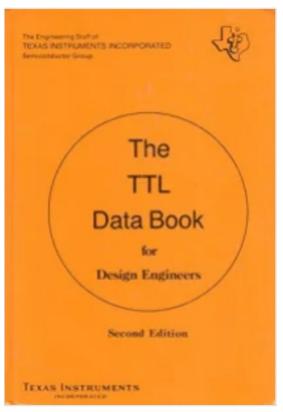

The TTL Data Book for Design Engineers.

By always ensuring any bill of materials included at least one TTL part that was only available from it, Texas Instruments was able to stay one step ahead of the competition and own the T'TL market for the best part of 30 years, until standard logic eventually fell victim to the 1980s application-specific IC revolution.

Charles Sporck, Noyce's operations manager often credited with running the industry's tightest ship, left in early 1968 along with Pierre Lamond to join Widlar and Talbert at National Semiconductor. That triggered Noyce and Moore's departure from the firm later that same year−a pivotal moment in the eventual demise of the firm. The collective exodus of Sporck, Noyce, and Moore, along with so many other executives, signaled the end of an era, prompting Sherman Fairchild to bring in a new management team, led by C. Lester Hogan, then vice president of Motorola Semiconductor.

Sporck → National

#### **HOGAN'S HEROES**

Hogan's arrival, and the subsequent displacement of Fairchild managers, demoralized the firm even further, prompting a further exodus of employees who would launch a host of new companies. Leading a group dubbed "Hogan's Heroes," the ultra-conservative Motorola executives immediately clashed with Sanders, Fairchild's flamboyant sales chief.

Hogan/Wilf/Sanders

While initially slow to respond to the changing market under Sander's direction, Fairchild embarked on a strategy of leapfrogging Texas Instruments by focusing on more complex large scale, 30-plus gate parts, instead of simpler small and medium scale devices under 30 gates — a strategy that was proving popular and successful with engineers. The move forced Texas Instruments to recognize the threat and copy all of Fairchild's 9300 series parts under 74 series numbers (for example the 9300 became the 74195 and the 9341 the 74181.)

Sander's entire strategy collapsed, however, when Hogan capitulated to Ken Olsen, founder and CEO of Digital Equipment Corporation and a key Fairchild customer. Olsen wanted Fairchild to give up on its proprietary TTL technology and instead second-source Texas Instruments' 74 Series TTL. Against Sanders' wishes, Hogan agreed, signing the death warrant for Fairchild's TTL strategy. Sanders was, understandably livid. "You've just killed the company, Ken," Sander's fumed.

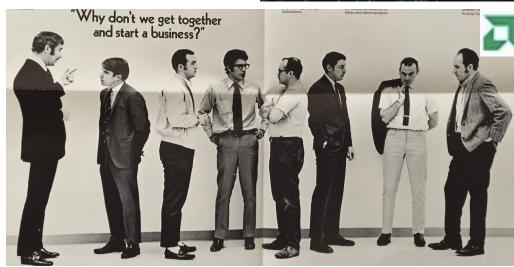

Hogan's betrayal was the last straw for Sanders. He, together with a group of Fairchild engineers, quit to start Advanced Micro Devices. With Sanders installed as president, one of his first moves was to establish the mantra: "People first, revenues and profits will follow." Sanders also gave every employee stock options in the new company, an innovation at the time.

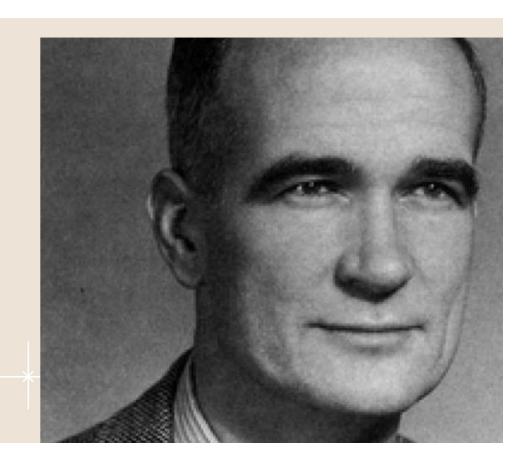

#### **Bell Labs**

### Founders HoF

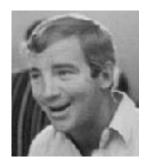

**Wm Shockley**

**Jerry Sanders**

CEO, AMD

AMD cofounder

**Jack Gifford**

In 1983, Gifford cofounded Maxim Integrated **Products**

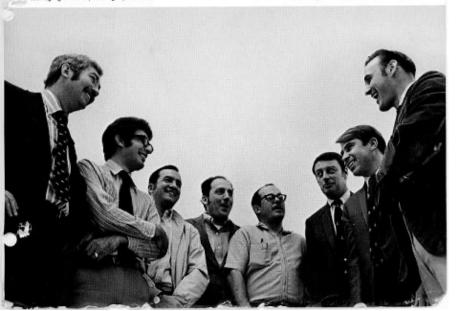

1969-2002 From left: W. Jerry Sanders III, President and Chairman of the Board. D. John Carey, Managing Director of Complex Digital Operations. Svin E. Simonsen, Director of Engineering, Complex Digital Operations, Frank T. Botte, Director Development, Analog Operations, James R. Giller, Oirector of Engineering, Analog Operations, Eduar J. Turney, Director of Sales and Administration. Josc F. Gifford, Director of Markating and Business Development, R. Lawrence Stonger, Managing Director, Analog Operations.

Fairchild Chairman/CEO, LSI Logic founder

Cypress Semi founder

### Intel

#### 1968

### **Intel Originals**

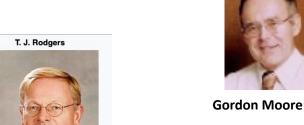

L to R: **Andy Grove Bob Noyce** Gordon Moore

> Founders: **Bob Noyce** Gordon Moore

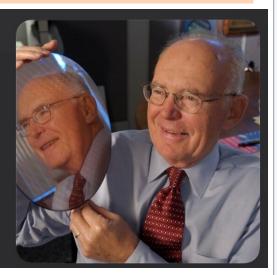

### Intel CEO Gordon Moore

Screenshot of Gordon Moore featured in Scientists You Must Know by the Science History Institute. Courtesy of the Science History Institute.

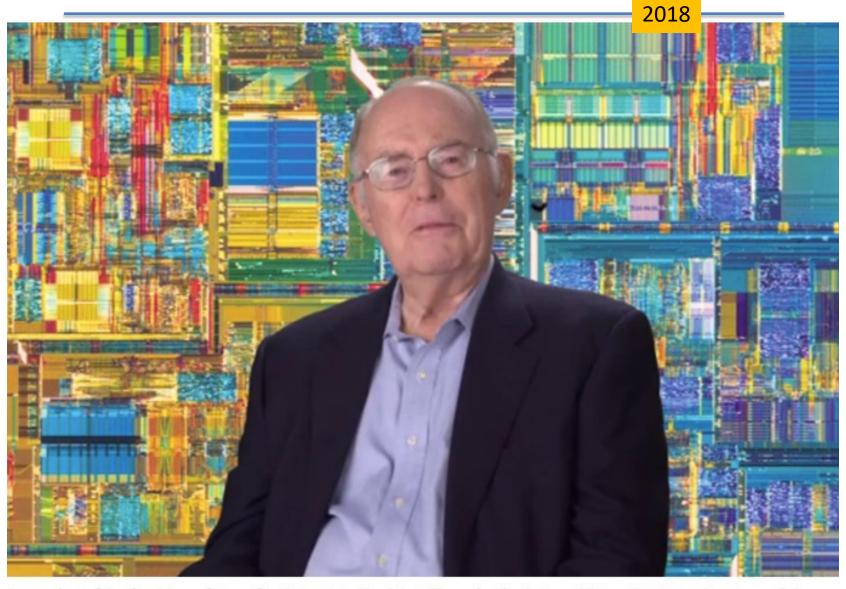

# Intel CEO Andy Grove

Andy Grove was Intel's feisty CEO successor to Bob Noyce, hence 2nd one. Andy reigned over Intel in the 1980's. Andy battled AMD's CEO Jerry Sanders over the rights to the i80386 chip design awarded by the legendary 2nd source contract -- culminating in a \$1B lawsuit by AMD.

Source: VentureBeat

"Bad Companies Are Destroyed by Crises ... Great Companies Are Improved by Them"

AMD

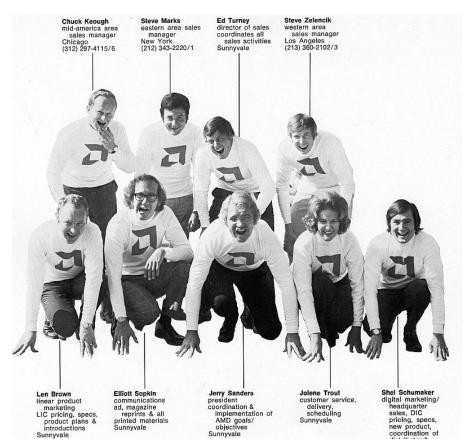

distributor & international activities Sunnyvale

Jeff Drobman ©2016-23

From left: W. Jerry Sanders III, President and Chairman of the Board. D. John Carey, Managing Director of Complex Digital Operations. Sven E. Simonsen, Director of Engineering, Complex Digital Operations, Frank T. Botte, Director of Development, Analog Operations, James N. Giles, Director of Engineering, Analog Operations, Edwin J. Turney, Director of Sales and Administration, Jack F. Gifford, Director of Marketing and Business Development, R. Lawrence Stenger, Managing Director, Analog Operations.

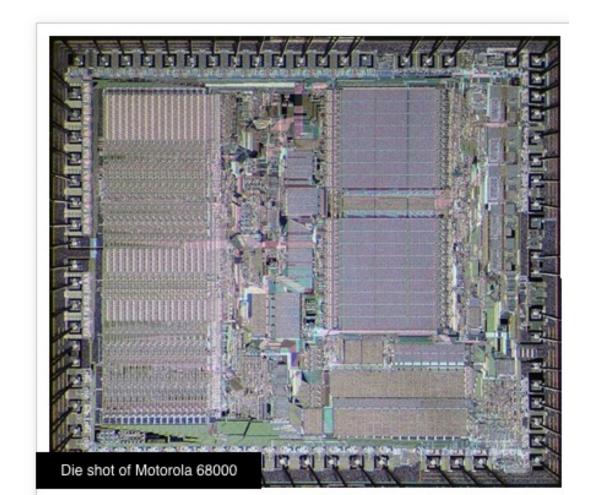

Motorola was a major chip company, having pioneered in digital logic and microprocessors such as the 6800/68000 and PPC. but Motorola no longer exists. it was first split into 2 companies: Motorola Solutions and Motorola Mobility, in 2011 (sold to Google in 2012, then to Lenovo in 2014). that was after the chip business was split up: ON Semi in 1999, and then Freescale in 2004, which was then sold to NXP Semi (Philips) in 2015.

|   | Fate       | Demerged into Motorola Mobility and<br>Motorola Solutions in 2011                                                        |  |  |

|---|------------|--------------------------------------------------------------------------------------------------------------------------|--|--|

| L | Successors | Motorola Mobility Motorola Solutions NXP Semiconductors ON Semiconductor CommScope (General Instrument) Cambium Networks |  |  |

| า | Founded    | September 25, 1928; 92 years ago                                                                                         |  |  |

| ) | Founders   | Paul and Joseph Galvin                                                                                                   |  |  |

|   | Defunct    | January 4, 2011; 10 years ago                                                                                            |  |  |

#### from Wikipedia:

Motorola, Inc. (/\_mootə'roolə/[2]) was an American multinational telecommunications company founded on September 25, 1928, based in Schaumburg, Illinois. After having lost \$4.3 billion from 2007 to 2009, the company demerged into two independent public companies, Motorola Mobility and Motorola Solutions on January 4, 2011.[3] Motorola Inc. was renamed Motorola Solutions and is legally the direct successor to the original company after the demerger from Motorola Mobility.[4][5] Motorola Mobility was sold to Google in 2012, and acquired by Chinese company Lenovo in 2014

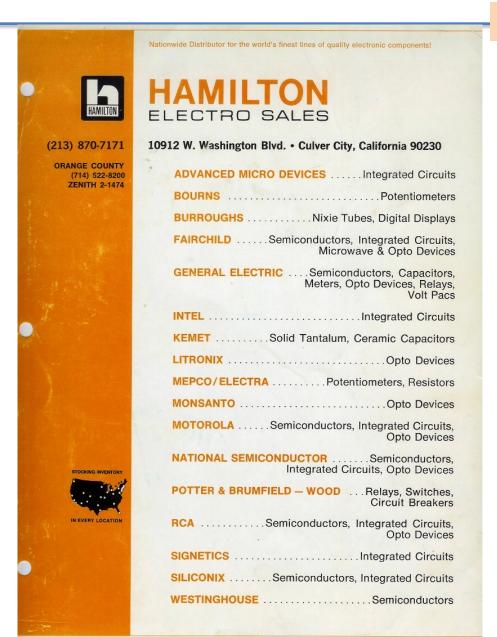

### Electronic Device Cos.

1972

# Chips on a PCB

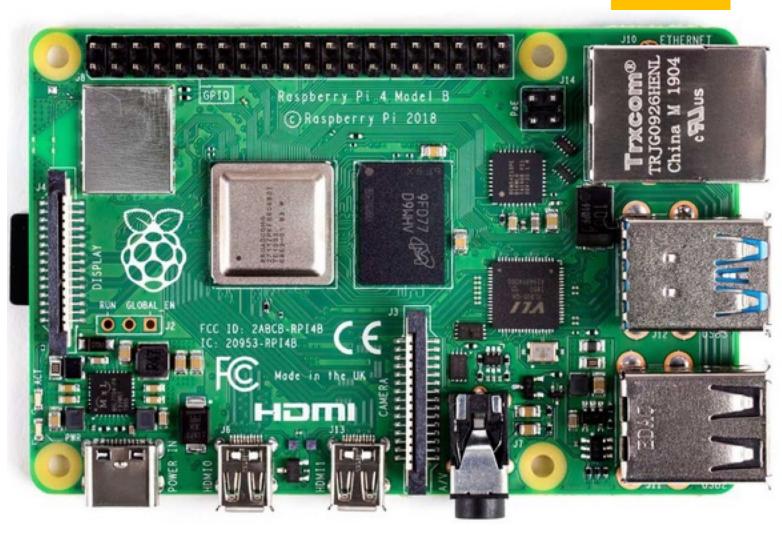

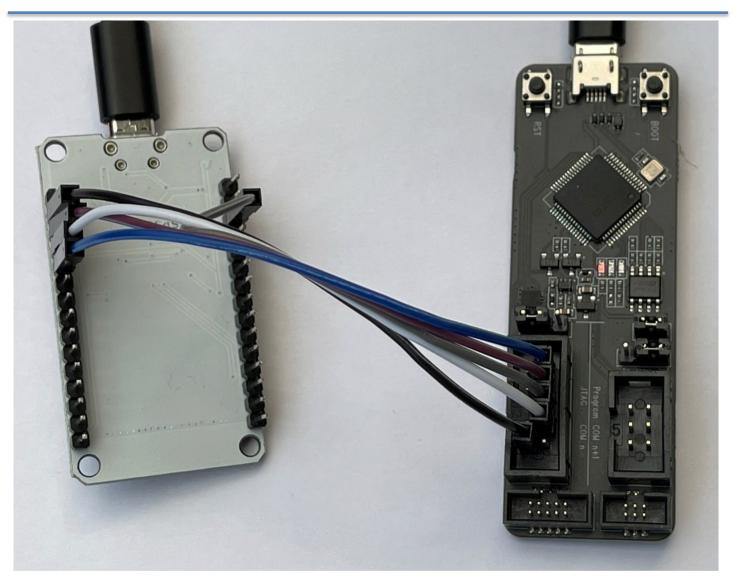

### **Dev Boards**

#### POPULAR DEVELOPMENT BOARDS

The SoCKit Development Kit presents a robust hardware design platform built around the Altera System-on-Chip (SoC) FPGA, which combines the latest dual-core Cortex-A9 embedded cores with industry-leading programmable logic for ultimate design flexibility

#### MAX1000 IOT Maker Board

For engineers designing compact smart solutions for the IoT market, this FPGA IoT Maker Board is an excellent tool to speed up the development process and enter the market with a high-performance, reliable product.

#### **Google Coral Dev Board**

The Coral Dev Board is now in-stock and available for free 1-day shipping at Arrow.com. Prototype, scale, and deploy with more flexibility using the Coral Dev Board and accessories with Google.

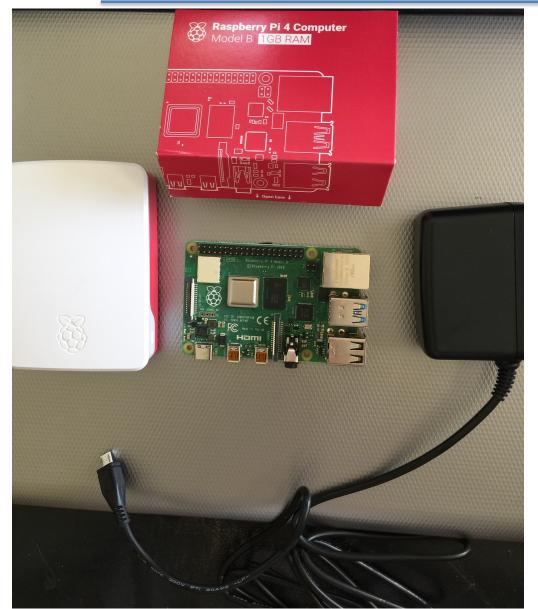

# ARM-A72 Development Boar Soft NOIEAPPO

# Chips

# Microprocessors MPU/MCU

# Early MPUs

YOU THOUGHT IT STARTED WITH THE INTEL 4004, BUT THE TALE IS MORE Story of the

First

+++ By Ken Shirriff +++

### Microprocessors

TRANSISTORS, the electronic amplifiers and switches found at the heart of everything from pocket radios to warehouse-size supercomputers, were invented in 1947. Early devices were of a type called bipolar transistors, which are still in use. By the 1960s, engineers had figured out how to combine multiple bipolar transistors into single integrated circuits. But because of the complex structure of these transistors, an integrated circuit could contain only a small number of them. So although a minicomputer built from bipolar integrated circuits was much smaller than earlier computers, it still required multiple boards with hundreds of chips. ¶ In 1960, a new type of transistor was demonstrated: the metal-oxide-semiconductor (MOS) transistor. At first this technology wasn't all that promising. These transistors were slower, less reliable, and more expensive than their bipolar counterparts. But by 1964, integrated circuits based on MOS transistors boasted higher densities and lower manufacturing costs than those of the bipolar competition. Integrated circuits continued to increase in complexity, as described by Moore's Law, but now MOS technology took the lead.

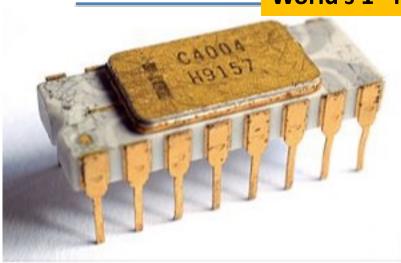

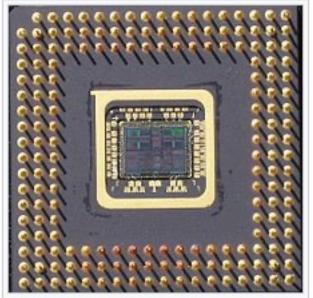

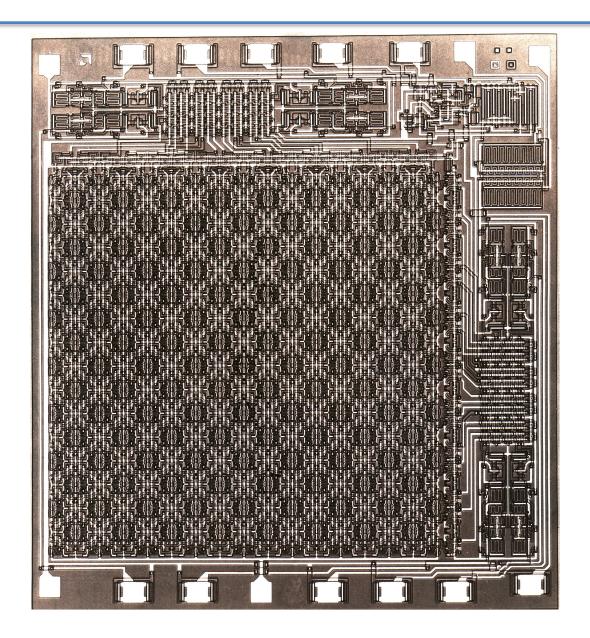

### Intel i4004 and i1103A

World's 1st MPU & DRAM

The Intel 4004 is a 4-bit central processing unit (CPU) released by Intel Corporation in 1971. It was the first commercially available microprocessor, and the first in a long line of Intel CPUs. The chip design, implemented with the MOS silicon gate technology, started in April 1970, and was created by Feder

1<sup>st</sup> MPU

4-bit

1971

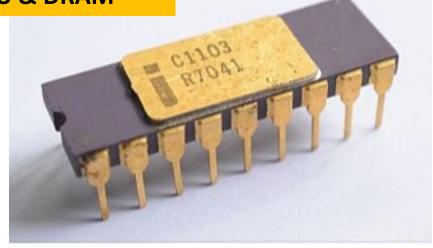

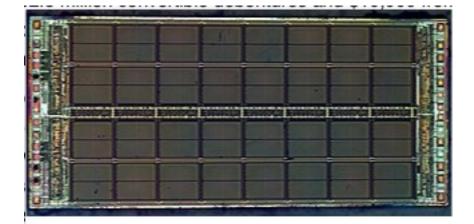

The 1103 is a dynamic random-access memory (DRAM) integrated circuit (IC) developed and fabricated by Intel. Introduced in October 1970, the 1103 was the first commercially available DRAM IC; and due to its small physical size and low price relative to magnetic-core memory, it replaced the

1<sup>st</sup> DRAM

1K x1

1970

# Intel i8008

#### World's 1st 8-bit MPU

The venerable 16-pin side-brazed DIP. (Click image to view full size)

1971 **DIP**

# Intel i4004/i8008

### World's 1st 4/8-bit MPU's

8008 3098 transistors

Intel MCS-4 and MCS-8 design team and CPU chips

# Intel i4004/i8008

World's 1<sup>st</sup> 4/8-bit MPU's

TMX 1795 3,078 transistors

1 mm

EVERYTHING'S BIGGER IN TEXAS: Although Texas Instruments'

TMX 1795 and Intel's 8008 had a similar number of transistors, the

former required a much larger silicon die. Indeed, the TMX 1795 was

larger than the Intel 8008 and 4004 combined. Intel's engineers

believed that its large size made the TI chip impractical to produce in

commercial quantities, but TI's very successful TMS 0100 calculator

chip, introduced at about the same time, had an even larger die. So the

connection between die size and commercial viability must not have

been straightforward.

4004 2,300 transistors

8008 3,098 transistors

#### Wikipedia

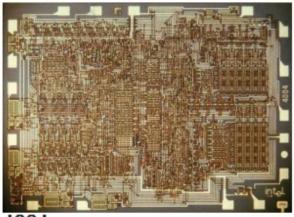

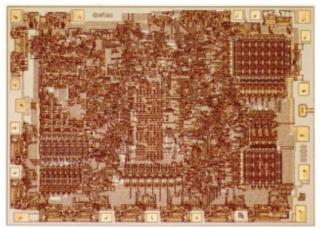

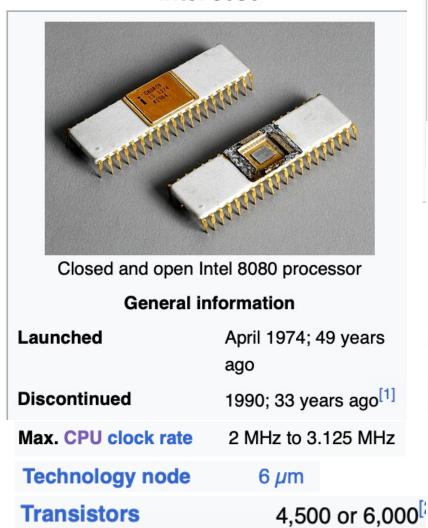

### 8-bit i8080

#### Intel 8080

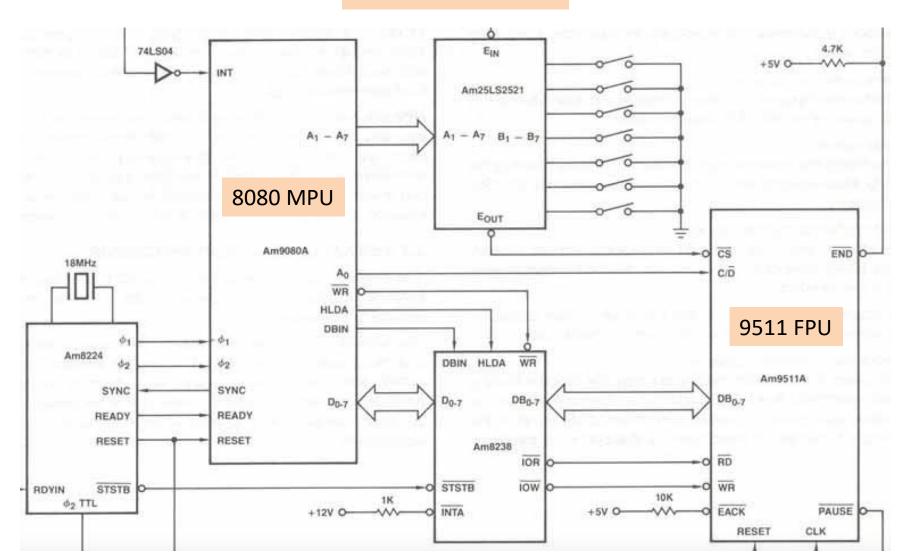

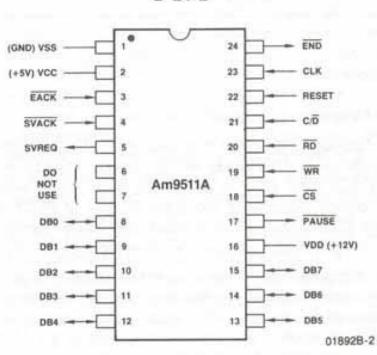

AMD 8080 clone (Am9080) 13GAO8OCMAF C80804 7723MP CONNECTION DIAGRAM Top View D-24-2 AMD Am9511 FPU) (GND) VSS 23 EACK 22 SVACK SVREQ 19 DO Am9511A PAUSE VDD (+12V) 15 **DB2** 14 DB3 13

# Venerable Zilog Z80

- ❖ Improved i8080 (dual register bank, for one)

- ❖ Spinoff of Intel (Federico Faggin, Bernard Peuto, et al.

### AMD FPU

Am9511/12

From AMD datasheet

Single & Double precision **Floating-point** with *transcendentals*

# Floating Point Processor Manual Am9511A/Am9512

### AMD FPU

Am9511/12

From AMD datasheet

Single & Double precision **Floating-point** with *transcendentals*

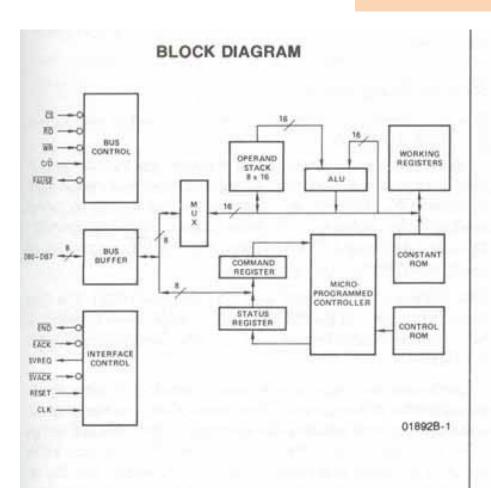

### 5.2 Am9511A ARITHMETIC PROCESSOR

This pioneer single-chip arithmetic processor interfaces with most popular 8-bit microprocessors such as Am9080A, Am8085, MC6800 by Motorola and Z80 by Zilog. It can also be used for 16-bit microprocessors such as AmZ8000,\* but its performance with such 16-bit microprocessors is somewhat hindered by its 8-bit external data bus.

Although the external interface is only 8 bits wide, the Am9511A internally is a 16-bit microprogrammed, stack-oriented floating point machine. It includes not only floating point operations but fixed point as well. In addition to the basic add, subtract, multiply and divide operations, transcendental derived functions are also included. A data sheet of Am9511A is included in Appendix A.

### **AMD FPU Interface**

Am9511/12

From AMD datasheet

### **AMD FPU**

### Am9511/12

#### From AMD datasheet

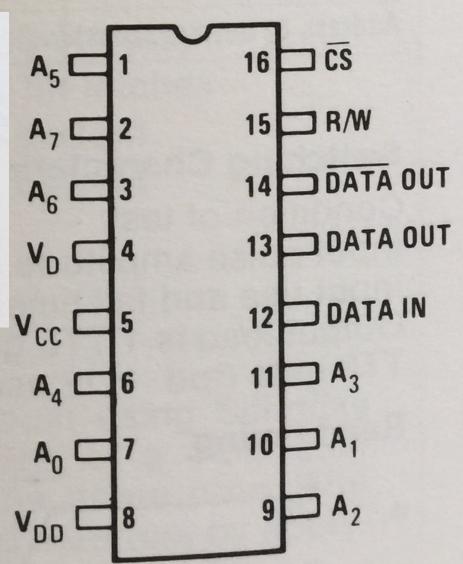

#### CONNECTION DIAGRAM Top View D-24-2

Note: Pin 1 is marked for orientation.

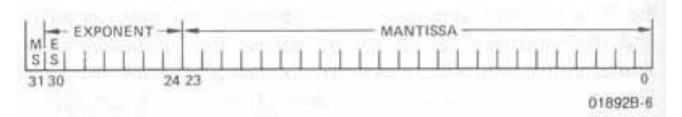

### **AMD FPU Format**

### Am9511/12

From AMD datasheet

#### FLOATING POINT FORMAT

The format for floating-point values in the Am9511A is given below. The mantissa is expressed as a 24-bit (fractional) value; the exponent is expressed as an unbiased two's complement 7-bit value having a range of -64 to +63. The most significant bit is the sign of the mantissa (0 = positive, 1 = negative), for a total of 32 bits. The binary point is assumed to be to the left of the most significant mantissa bit (bit 23). All floating-point data values must be normalized. Bit 23 must be equal to 1, except for the value zero, which is represented by all zeros.

The range of values that can be represented in this format is  $\pm (2.7 \times 10^{-20} \text{ to } 9.2 \times 10^{18})$  and zero.

### **AMD FPU Instructions**

### Am9511/12

From AMD datasheet

#### Command Mnemonics in Alphabetical Order.

| ACOS | ARCCOSINE             | LOG  | COMMON LOGARITHM                  |

|------|-----------------------|------|-----------------------------------|

| ASIN | ARCSINE               | LN   | NATURAL LOGARITHM                 |

| ATAN | ARCTANGENT            | NOP  | NO OPERATION                      |

| CHSD | CHANGE SIGN DOUBLE    | POPD | POP STACK DOUBLE                  |

| CHSF | CHANGE SIGN FLOATING  | POPF | POP STACK FLOATING                |

| CHSS | CHANGE SIGN SINGLE    | POPS | POP STACK SINGLE                  |

| cos  | COSINE                | PTOD | PUSH STACK DOUBLE                 |

| DADD | DOUBLE ADD            | PTOF | PUSH STACK FLOATING               |

| DDIV | DOUBLE DIVIDE         | PTOS | PUSH STACK SINGLE                 |

| DMUL | DOUBLE MULTIPLY LOWER | PUPI | PUSH π                            |

| DMUU | DOUBLE MULTIPLY UPPER | PWR  | POWER (XY)                        |

| DSUB | DOUBLE SUBTRACT       | SADD | SINGLE ADD                        |

| EXP  | EXPONENTIATION (ex)   | SDIV | SINGLE DIVIDE                     |

| FADD | FLOATING ADD          | SIN  | SINE                              |

| FDIV | FLOATING DIVIDE       | SMUL | SINGLE MULTIPLY LOWER             |

| FIXD | FIX DOUBLE            | SMUU | SINGLE MULTIPLY UPPER             |

| FIXS | FIX SINGLE            | SQRT | SQUARE ROOT                       |

| FLTD | FLOAT DOUBLE          | SSUB | SINGLE SUBTRACT                   |

| FLTS | FLOAT SINGLE          | TAN  | TANGENT                           |

| FMUL | FLOATING MULTIPLY     | XCHD | EXCHANGE OPERANDS DOUBLE          |

| FSUB | FLOATING SUBTRACT     | XCHF | <b>EXCHANGE OPERANDS FLOATING</b> |

|      |                       | XCHS | <b>EXCHANGE OPERANDS SINGLE</b>   |

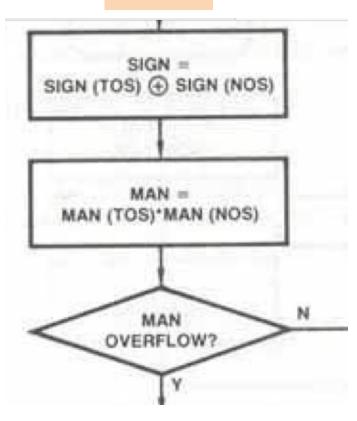

### **FMUL** AMD FPU Flow TOS = 0?Zero? NOS = 07 UNPACK TOS & NOS EXP (TOS) = Exponent EXP (TOS) - 12710 EXP (NOS) = EXP (NOS) - 12710 EXP = EXP (TOS) + EXP (NOS) OVERFLOW?

#### DR JEFF Jeff Drobman ©2016-23

Am9511/12

From AMD datasheet

Mantissa

# i8086 History

WikiSemi

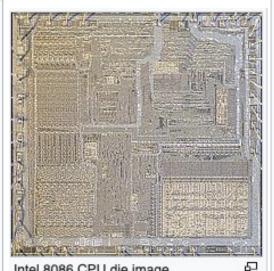

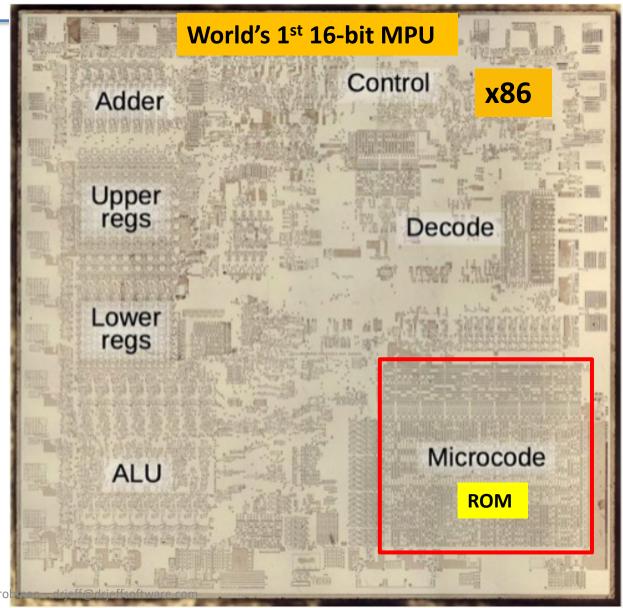

#### History of the 8086

The path to the 8086 was not as direct and planned as you might expect. Its earliest ancestor was the Datapoint 2200, a desktop computer/terminal from 1970. The Datapoint 2200 was before the creation of the microprocessor, so it used an 8-bit processor built from a board full of individual TTL integrated circuits. Datapoint asked Intel and Texas Instruments if it would be possible to replace that board of chips with a single chip. Copying the Datapoint 2200's architecture, Texas Instruments created the TMX 1795 processor (1971) and Intel created the 8008 processor (1972). However, Datapoint rejected these processors, a fateful decision. Although Texas Instruments couldn't find a customer for the TMX 1795 processor and abandoned it, Intel decided to sell the 8008 as a product, creating the microprocessor market. Intel followed the 8008 with the improved 8080 (1974) and 8085 (1976) processors. (I've written more about early microprocessors here.)

Datapoint 2200 computer. Photo courtesy of Austin Roche.

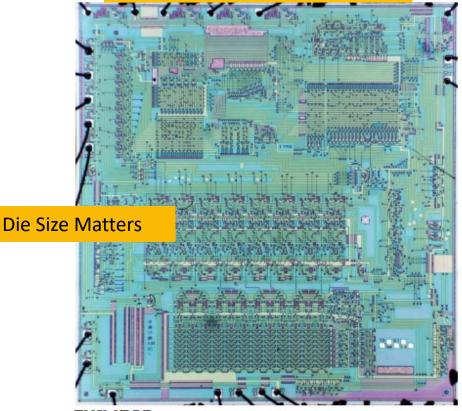

# i8086 History

WikiSemi

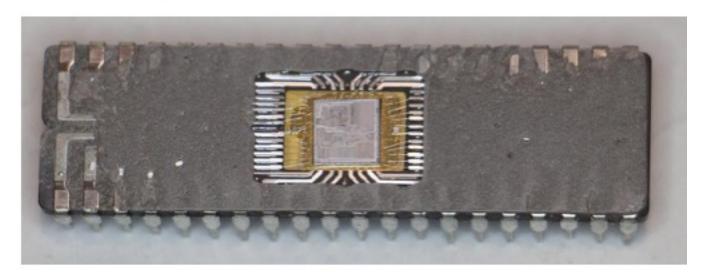

#### Microcode

One of the hardest parts of computer design is creating the control logic that tells each part of the processor what to do to carry out each instruction. In 1951, Maurice Wilkes came up with the idea of microcode: instead of building the control logic from complex logic gate circuitry, the control logic could be replaced with special code called microcode. To execute an instruction, the computer internally executes several simpler micro-instructions, which are specified by the microcode. With microcode, building the processor's control logic becomes a programming task instead of a logic design task.

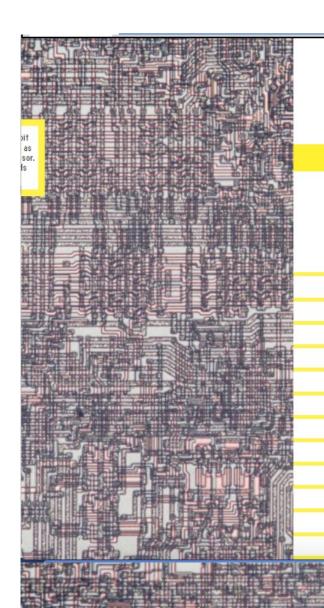

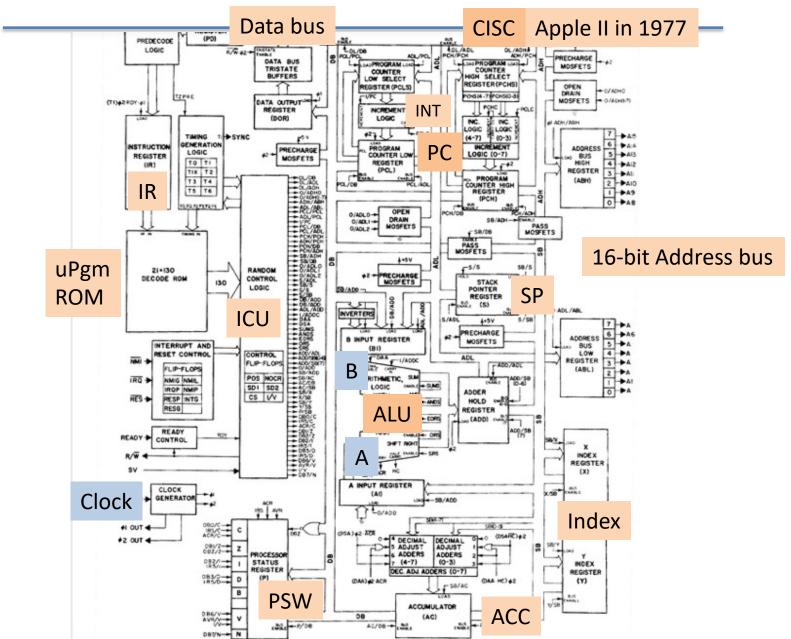

Microcode was common in mainframe computers of the 1960s, but early microprocessors such as the 6502 and Z-80 didn't use microcode because early chips didn't have room to store microcode. However, later chips such as the 8086 and 68000, used microcode, taking advantage of increasing chip densities. This allowed the 8086 to implement complex instructions (such as multiplication and string copying) without making the circuitry more complex. The downside was the microcode took a large fraction of the 8086's die; the microcode is visible in the lower-right corner of the die photos.3

| A BRAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                       | add a     | 8. 49444 P 8 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A PROPERTY OF THE PROPERTY OF |                       | MARAN     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SERRE RESE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PRESENT BERRE         | M M · MM  | in added de de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | A RESIDENCE OF STREET | AND PA    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AM M WW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                       |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A AA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | A AA A                | A . A     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       | MA MA     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       | M M M M M |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       | -         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |